Copyright © Siemens AG 2016. All rights reserved

416

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

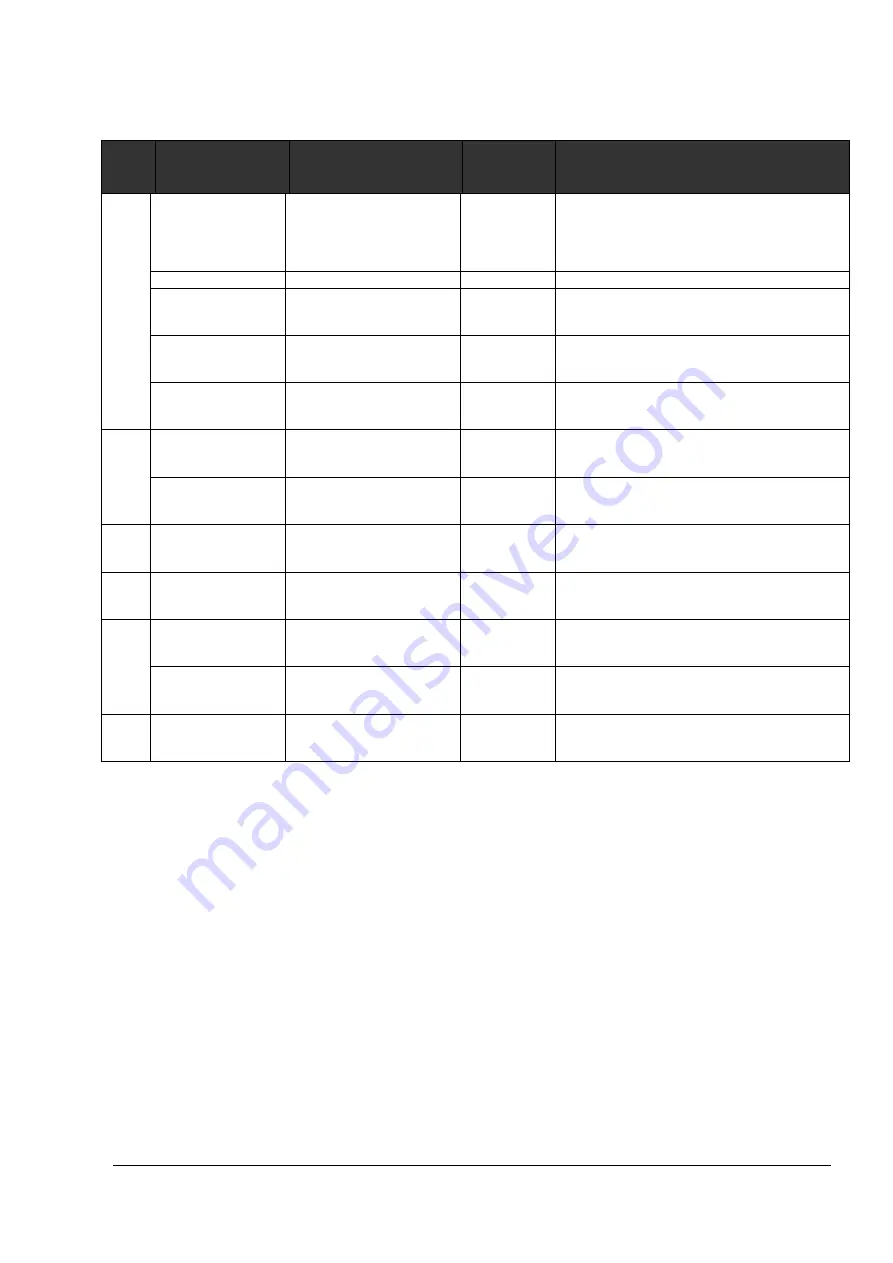

2.4.2 ARM926-D Memory Mapping

Seg

Address-Range

Memory/

Peripheral

Size /Byte

Description

0

0x0

000_0000h

...

0x0

000_1FFFh

0x0

3FF_FFFFh

Boot ROM (8 KByte)

EMC (64 MByte)

8 KByte

64 MByte

MEM_SWAP parameter assignment:

00b: -> Boot ROM (0 - 8 KByte), imaged

F

01b: -> EMC-SDRAM (0 - 64 MByte)

F

10b: -> EMC asyn memory (0 - 64 MByte)

11b: -> QVZ Error

0x0

404_0000h

...

0x0

7FF_FFFFh

Not used

< 64 MByte

0x0

800_0000h

...

0x0

803_FFFFh

ARM926 D-TCM

256 KByte

ARM 926 D-TCM (0 – 256 KByte physical. /

Step 64 KByte; not imaged)

F

0x0

804_0000h

...

0x0

FFF_FFFFh

Not used

< 128 MByte

1

0x1

000_0000h

...

0x1

10F_FFFFh

AHB peripherals

17

MByte

0x1

110_0000h

...

0x1

FFF_FFFFh

Not used

239 MByte

2

0x2

000_0000h

...

0x2

FFF_FFFFh

EMC SDRAM

(256 MByte)

256

MByte

3

0x3

000_0000h

...

0x3

FFF_FFFFh

EMC Asyn

Memory

256

MByte

4

0x4

000_0000h

...

0x4

05F_FFFFh

APB peripherals

128

KByte

0x4

100_0000h

...

0x4

FFF_FFFFh

Not used

< 256 MByte

5-F

0x5

000_0000h

...

0XF

FFF_FFFFh

Not used

2816 MByte

9

After a reset, the boot ROM is at address 0. The first 64 MByte of EMC-SDRAM or EMC asyn memory (chip select

Bank0) can also be mapped to address 0 with the MEM_SWAP register in the SCRB (see 2.3.10.9.22).

10

After a reset, no memory is assigned to address 0. The first 64 MByte of EMC-SDRAM or EMC asyn memory (chip

select Bank0) can also be mapped to address 0 with the MEM_SWAP register in the SCRB (see 2.3.10.9.22).

11

The ARM926 D-TCM is 0 - 256 KByte (adjustable in 64 KByte increments) and can be shown at address 0x0800

0000h by the SW in the ARM926 coprocessor register CP15 c9. ARM926 then accesses its D-TCM and not the AHB in

this address range. Please note that ARM926 D-TCM can only be displayed in the ARM address area in increments of

2

n

. If, for example, a physical size of D-TCM = 192 KByte has been selected in 'TCM926_Map Register', ARM926 can

only assign D-TCM an address range of 256 KByte.