Clock generation

Details on the different clock modes

(c) Spectrum GmbH

81

Details on the different clock modes

Standard internal sampling clock (PLL)

The internal sampling clock is generated in default mode by a programmable high precision quartz. You need to select the clock mode by

the dedicated register shown in the table below:

The user does not have to care on how the desired sampling rate is generated by multiplying and dividing internally. You simply write the

desired sample rate to the according register shown in the table below and the driver makes all the necessary calculations. If you want to

make sure the sample rate has been set correctly you can also read out the register and the driver will give you back the sampling rate that

is matching your desired one best.

Independent of the used clock source it is possible to enable the clock output. The clock will be available on the external clock output connector

and can be used to synchronize external equipment with the board.

Example on writing and reading internal sampling rate

Minimum internal sampling rate

The minimum and the maximum internal sampling rates depend on the specific type of board. Both values can be found in the technical data

section of this manual.

Using Quartz2 with PLL (optional, M4i cards only)

In some cases it is necessary to use a special high precision frequency for sampling rate generation. For these applications all cards of the

M3i/M4i series can be equipped with a special customer quartz. Please contact Spectrum for details on available oscillators. If your card is

equipped with a second oscillator you can enable it for sampling rate generation with the following register:

The quartz 2 clock is routed through a PLL to allow the generation of sampling rates based on this reference clock. As with internal PLL mode

it’s also possible to program the clock mode first, set a desired sampling rate with the SPC_SAMPLERATE register and to read it back. The

result will then again be the best matching sampling rate.

Independent of the used clock source it is possible to enable the clock output. The clock will be available on the external clock output connector

and can be used to synchronize external equipment with the board.

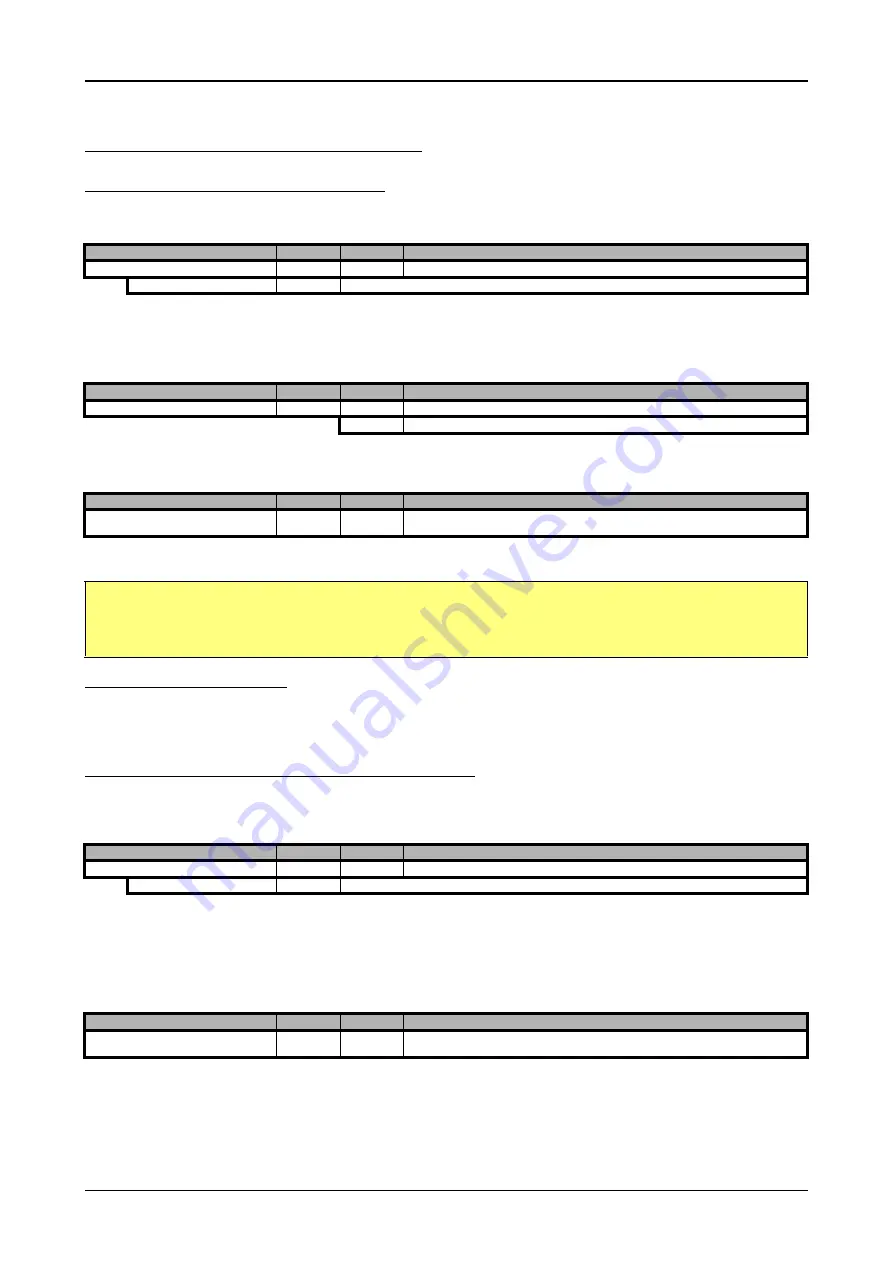

Register

Value

Direction

Description

SPC_CLOCKMODE

20200

read/write

Defines the used clock mode

SPC_CM_INTPLL

1

Enables internal programmable high precision Quartz 1 for sample clock generation

Register

Value

Direction

Description

SPC_SAMPLERATE

20000

write

Defines the sample rate in Hz for internal sample rate generation.

read

Read out the internal sample rate that is nearest matching to the desired one.

Register

Value

Direction

Description

SPC_CLOCKOUT

20110

read/write

Writing a „1“ enables clock output on external clock output connector. Writing a „0“ disables the

clock output (tristate)

spcm_dwSetParam_i32 (hDrv, SPC_CLOCKMODE, SPC_CM_INTPLL); // Enables internal programmable quartz 1

spcm_dwSetParam_i64 (hDrv, SPC_SAMPLERATE, 62500000); // Set internal sampling rate to 62.5 MHz

spcm_dwSetParam_i32 (hDrv, SPC_CLOCKOUT, 1); // enable the clock output of the card

spcm_dwGetParam_i64 (hDrv, SPC_SAMPLERATE, &lSamplerate); // Read back the programmed sample rate and print

printf („Sample rate = %d\n“, lSamplerate); // it. Output should be „Sample rate = 62500000“

Register

Value

Direction

Description

SPC_CLOCKMODE

20200

read/write

Defines the used clock mode

SPC_CM_QUARTZ2

4

Enables optional quartz2 for sample clock generation

Register

Value

Direction

Description

SPC_CLOCKOUT

20110

read/write

Writing a „1“ enables clock output on external clock output connector. Writing a „0“ disables the

clock output (tristate)