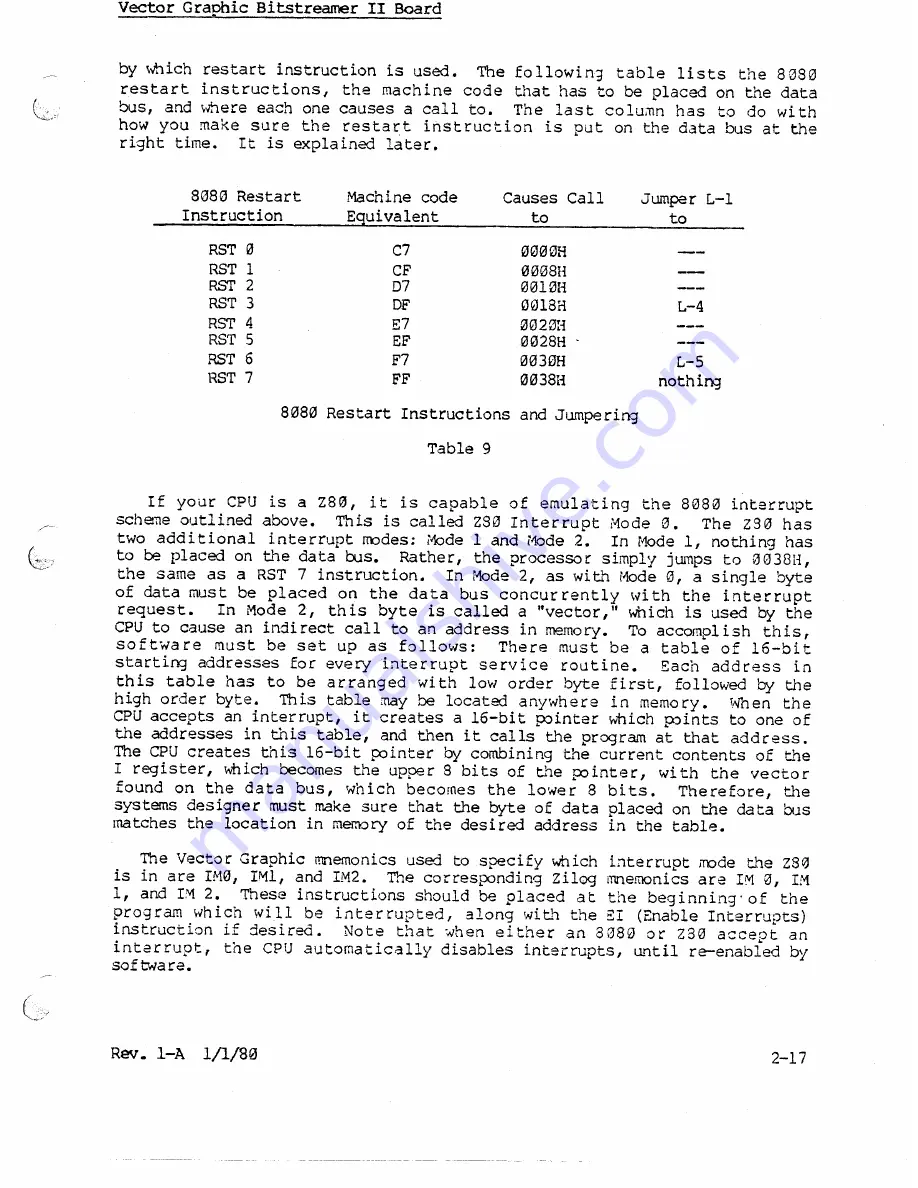

by \vhich restart

instruction

is used.

The

followin;

table

lists

the

8380

restart

instructions,

the

machine

code

that has

to be placed

on

the data

bus,

and \vhere each one causes

a call

to.

The

last

colu~n

has

to do

with

how

you

make

sure

the

restart

instruction

is put

on the data

bus at the

right

time.

It is explained

later.

8080

Restart

Machine

code

Causes

Call

Instruction

Equivalent

to

RST

10

C7

0000H

RST

I

CF

eJI0108B

RST 2

D7

0010H

RST3

OF

0018H

RST 4

E7

0020H

RST 5

EF

10028H

RST 6

F7

0030H

RST 7

FF

0038H

Jumper

L-l

to

L-S

nothi~

If your

CPU

is a Z80, it

is capable

of

emulating

the

8080 interrupt

schene

outlined

above.

This

is called

ZS0 Interrupt

Mode

0.

The

230 has

two

additional

interrupt

modes:

r~de

1 and (~de

2.

In Mode

1, nothing

has

to be placed

on the data

oos.

Rather,

the processor

simply

jumps

to

003811,

the

same

as a RST

7 instruction.

In r10de 2, as wi~,

Mode

0, a single

byte

of data must

be

placed

on

the

data

bus

concur rently

\Vith

the

interrupt

request.

In Mode

2,

this

byte

is called

a "vector,"

which

is used

by the

CPU to cause

an indirect

call

to an address

in memory.

To accomplish

this,

software

must

be

set

up

as

follows:

There

must

be

a table

of

16-bit

startir¥3 addresses

for every

interrupt

service

routine.

Each

address

in

this

table

has

to be

arranged

with

10Yl order

byte

first,

followed

by the

high

order

byte.

This

table may be located

anywhere

in memory.

When

the

CPU accepts

an interrupt,

it creates

a 16-bit

pointer

wnich

points

to one of

the addresses

in this

table,

and b,en

it calls

the program

at that

address.

The CPU creates

this 16-bit

pointer

by combining

the current

contents

of G~e

I register,

which

becomes

the upper

8 bits of t.'e pointer,

with

the

'./ector

found

on

the

data

bus,

'I'lhichbecomes

the

10'l'ler8 bits.

Therefore,

the

systems

designer

must make

sure

that the byte

of data

placed

on the data

OlS

matches

the location

in memory

of the desired

address

in the table.

The Vector

Graphic

mnemonics

used

to specify

which

interrupt

mode

G~e

280

is in are IMIO, IM1, and

1M2.

The corresponding

2i109

mnemonics

are

1M

0,

1M

1, and 1M 2.

These

instructions

should

be placed

at

the

beginning'

of

the

prog ram

wh ich

will

be

inter rupted,

along

IHit.l-)

the 81

(Enable Interrupts)

instruction

if desired.

Note

that

when

either

an

8080 or

230 accept

an

interrupt,

the

CPU

automatically

disables

interrupts,

Q~til

re-enabled

by

software.

Summary of Contents for Bitstreamer II

Page 1: ...lit t tiCAli1iC I JI U E I mAnUAL...

Page 2: ......

Page 3: ...BITSTREAMER II BOARD Revision 1 USER S MANUAL Revision A January 1 1980...

Page 6: ......

Page 8: ......

Page 18: ......

Page 19: ......

Page 24: ......

Page 46: ......

Page 50: ......

Page 52: ......

Page 53: ......

Page 54: ......