Legacy SPI Interface

EBX-11 Reference manual

67

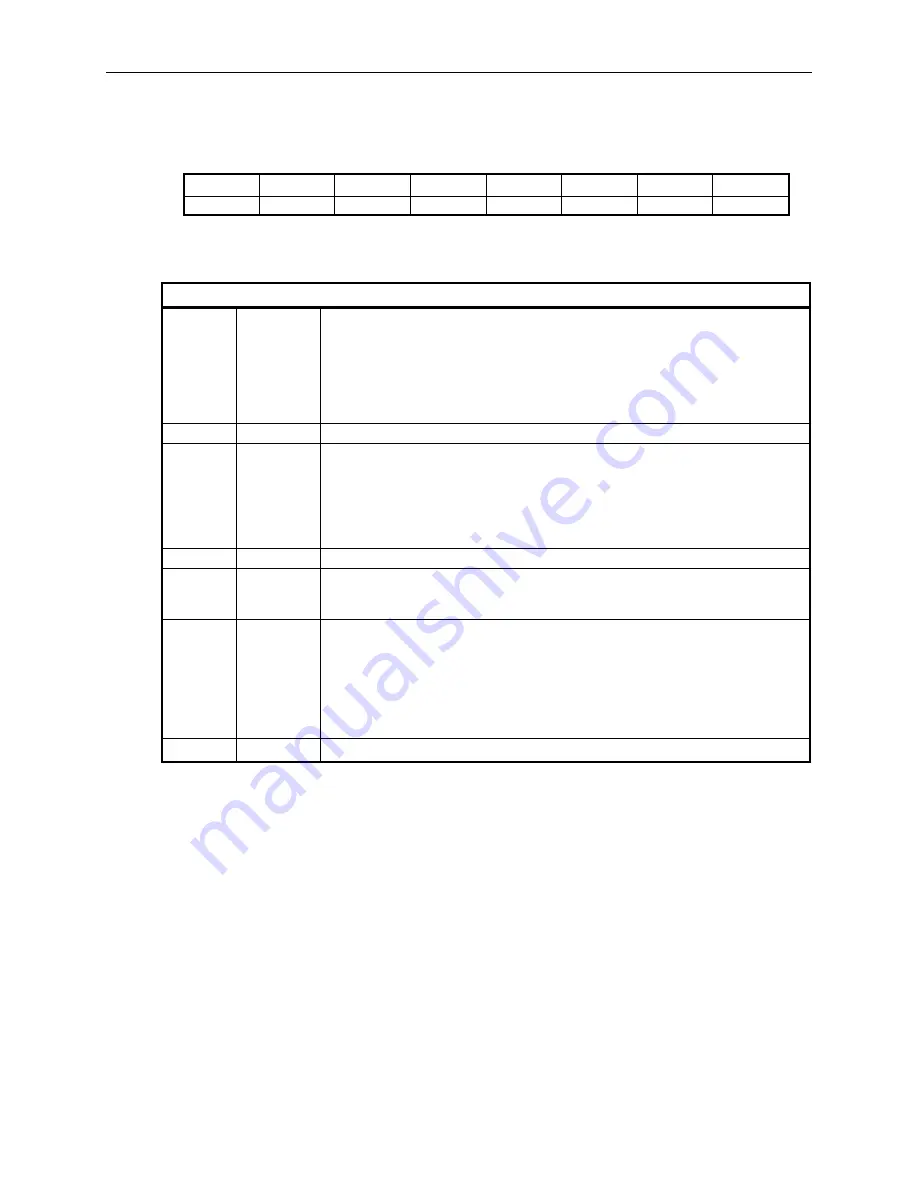

SPICON2 (READ/WRITE) 1D9h

D15

D14

D13

D12

D11

D10

D9

D8

INT1

Reserved

SPISET1

SPISET0

Reserved

DONE

CI

Reserved

Table 37: SPI Control Register 2 Bit assignments

Bit

Mnemonic

Description

D15

INT1

SPI Hardware Interrupt Enable

–

Setting this bit enables SPI devices with a

hardware interrupt feature to generate an interrupt request.

0 =

SPI device interrupts disabled

1 =

SPI device interrupts enabled

This IRQ is shared among all SPI devices on-board and connected to the

EBX-11.

D14

–

Reserved

– This bit is unused and read as 1.

D13-D12

SPISET

SPI Frame Length Control

–

These bits set the SPI cycle frame length.

SPISET1 SPISET0 Frame Length

0

0

8 Bit

0

1

16 Bit

1

0

Invalid

1

1

24 Bit

D11

–

Reserved

– This bit is unused and read as 1.

D10

DONE

SPI Cycle Complete Flag

–

Set by hardware on completion of every SPI bus

transaction. Cleared by writing a 0 to this bit or by hardware on initiation of a

new SPI transaction.

D9

CI

SPI Clock Idle

–

CI along with CP in SPICON1 combine to set the SCLK

behavior.

CI CP SCLK

1

0

Idle low, rising edge active

1

1

Idle low, falling edge active

0

1

Idle high, rising edge active

0

0

Idle high, falling edge active

D8

–

Reserved

– This bit is unused and read as 1.

StockCheck.com