DS593 (v1.2.1) March 17, 2011

PN 0011051 04

1

© Copyright 2008–2011 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and

other countries. All other trademarks are the property of their respective owners.

Features

•

High-performance FPGA and PROM programming and

configuration

•

Includes innovative FPGA-based acceleration

firmware encapsulated in a small form factor pod

attached to the cable

•

Leverages high-speed Slave Serial mode

programming interface

•

Recommended for prototyping use only

•

Easy to use

•

Fully integrated and optimized for use with Xilinx®

iMPACT software

•

Intuitive multiple cable management from a single

application

•

Supported on the following operating systems:

-

Microsoft Windows XP Professional

-

Microsoft Windows Vista

-

Red Hat Enterprise Linux

-

SUSE Linux Enterprise

•

Automatically senses and adapts to target I/O

voltage

•

Interfaces to devices operating at 5V (TTL), 3.3V

(LVCMOS), 2.5V, 1.8V and 1.5V

•

Intuitive flyleads-to-cable interface labeling

•

Reliable

•

Backwards compatibility with Platform Cable USB,

including Pb-Free (RoHS-compliant)

•

USB Integrators Forum (USB-IF) certified

•

CE and FCC compliant

•

Leverages industry standards, including JTAG

Boundary-Scan IEEE 1149.1, SPI and USB 2.0

•

Programs and configures all Xilinx devices

•

XC18V00 ISP PROMs

•

Platform Flash XCF00S/XCF00P/XL PROMs

•

All Virtex®, Spartan® and XC4000 FPGA families

•

XC9500 / XC9500XL / XC9500XV and

CoolRunner™ XPLA3 / CoolRunner-II CPLDs

Note:

Xilinx iMPACT software is required for

programming and configuration

•

Third-party PROM device programming support

•

Directly programs selected Serial Peripheral

Interface (SPI) flash memory devices

•

Indirectly programs selected SPI or parallel flash

memory devices via FPGA JTAG port

•

Highly optimized for use with Xilinx design tools

•

ISE® Foundation™ Software

•

Embedded Development Kit

•

ChipScope™ Pro Analyzer

•

System Generator for DSP

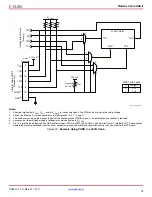

Platform Cable USB II Description

Much more than just a simple USB cable, Platform Cable

USB II (

) provides integrated firmware (hardware

and software) to deliver high-performance, reliable and

easy-to-perform configuration of Xilinx devices.

Platform Cable USB II attaches to user hardware for the

purpose of configuring Xilinx FPGAs, programming Xilinx

PROMs and CPLDs, and directly programming third-party

SPI flash devices. In addition, the cable provides a means of

indirectly programming Platform Flash XL, third-party SPI

flash memory devices, and third-party parallel NOR flash

memory devices via the FPGA JTAG port. Furthermore,

Platform Cable USB II is a cost effective tool for debugging

embedded software and firmware when used with

applications such as Xilinx's Embedded Development Kit

and ChipScope Pro Analyzer.

Platform Cable USB II is an upgrade to and replaces

Platform Cable USB. Similar to its popular predecessor,

Platform Cable USB II is intended for prototyping

environments only. Platform Cable USB II is backwards

35

Platform Cable USB II

DS593 (v1.2.1) March 17, 2011