AXI Bridge for PCI Express v2.4

84

PG055 June 4, 2014

Chapter 5:

Example Design

provides a descriptions of the contents of the example design directories.

Table 5-1:

Example Design Structure

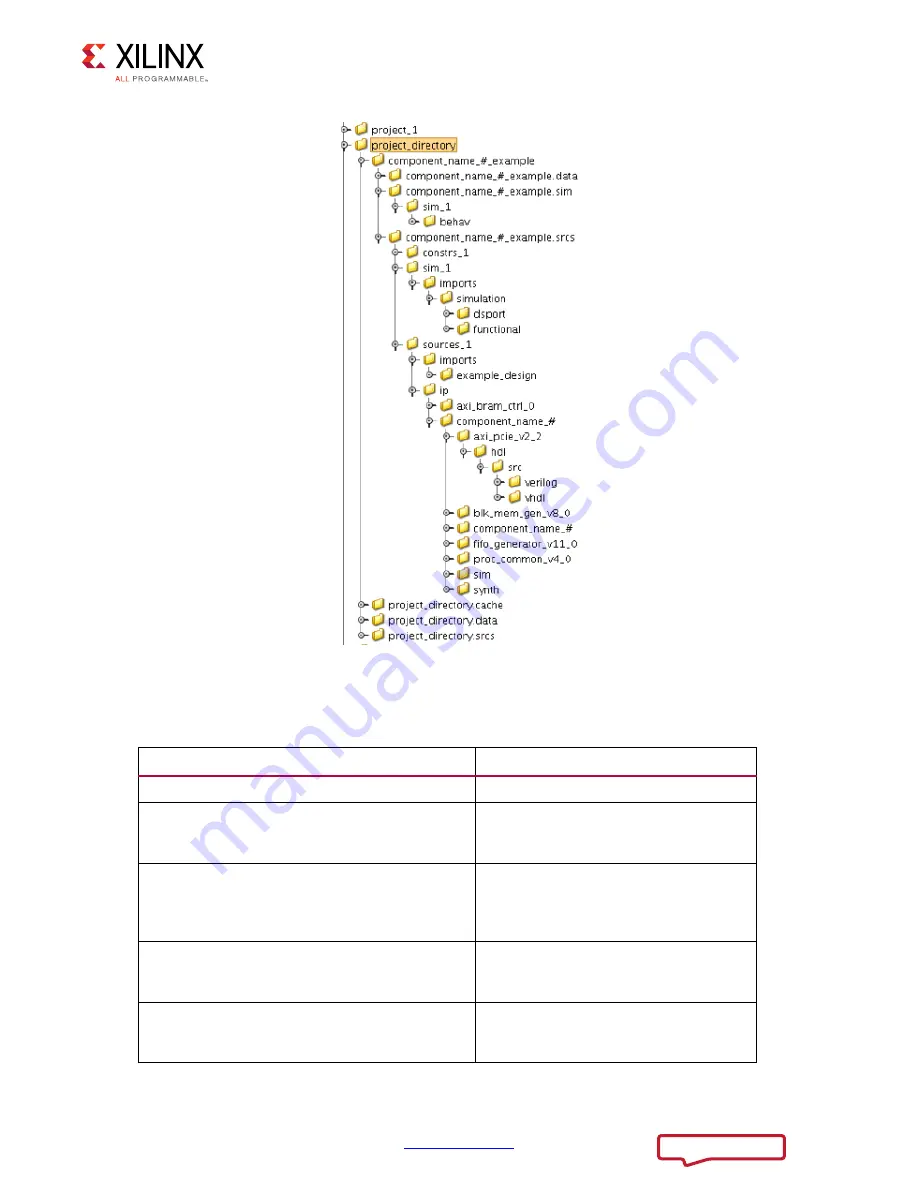

X-Ref Target - Figure 5-2

Figure 5-2:

Example Design Output Structure

Directory

Description

project_1/axi_pcie_0_example

Contains all example design files.

project_1/axi_pcie_0_example/

axi_pcie_0_example.srcs/sources_1/imports/

example_design/

Contains the top module for the

example design,

xilinx_axi_pcie_ep.v

.

project_1/axi_pcie_0_example/

axi_pcie_0_example.srcs/sources_1/ip/axi_pcie_0

Contains the XDC file based on device

selected, all design files and subcores

used in axi_pcie, and the top modules for

simulation and synthesis.

project_1/axi_pcie_0_example/

axi_pcie_0_example.srcs/sources_1/ip/

axi_bram_ctrl_0

Contains block RAM controller files used

in example design.

project_1/axi_pcie_0_example/

axi_pcie_0_example.srcs/sim_1/imports/

simulation/dsport

Contains all RP files, cgator and PIO files.