Virtex-6 FPGA System Monitor

15

UG370 (v1.1) June 14, 2010

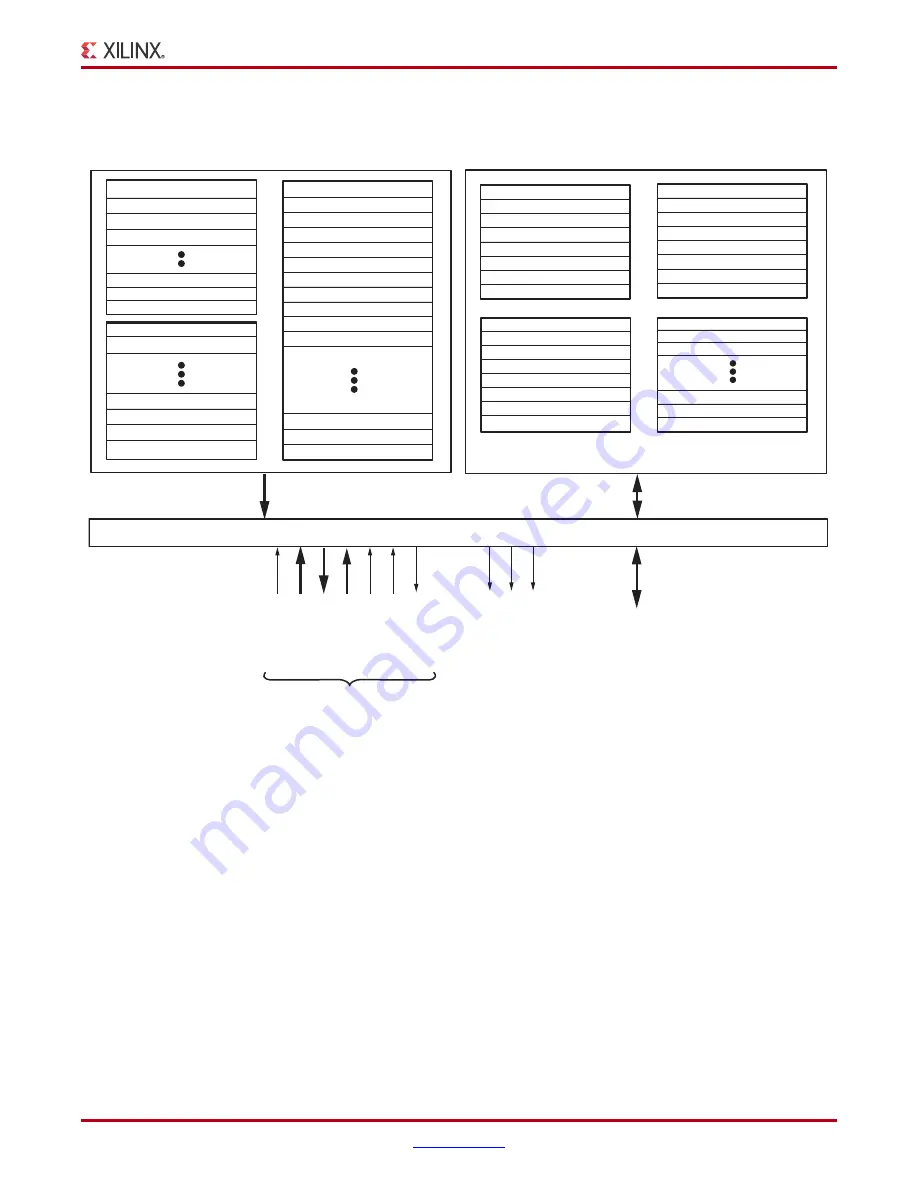

Register File Interface

Status Registers

The first 64 address locations (DADDR[6:0] =

00h

to

3Fh

) contain the status registers that

are Read-Only and cannot be initialized when System Monitor is instantiated in a design.

The status registers contain the results of an analog-to-digital conversion of the on-chip

sensors and external channels. All sensors and external analog-input channels have a

unique channel address (see

). The measurement result from each channel

is stored in a status register with the same address on the DRP.

For example, the result from an Analog-to-Digital Conversion on ADC multiplexer

channel 0 (temperature sensor) is stored in the Status Register at address

00h

. The result

from ADC mux channel 1 (V

CCINT

) is stored at address

01h

.

The status registers also store the maximum and minimum measurements recorded for the

on-chip sensors from the chip power-up or the

last user reset

of the System Monitor logic.

See

for a list of the status registers and definitions.

X-Ref Target - Figure 7

Figure 7:

System Monitor Register Interface

DI[15:0]

DO[15:0]

D

ADDR[6:0]

DCLK

JT

A

GB

USY

JT

A

GLOCKED

JT

A

GMODIFIED

DW

E

DEN

DRD

Y

Config Reg. #0 (40h)

Config Reg. #1 (41h)

Config Reg. #2 (42h)

Test Reg. #1 (44h)

Test Reg. #0 (43h)

Test Reg. #4 (47h)

Test Reg. #2 (45h)

Test Reg. #3 (46h)

Alarm Reg. #0 (50h)

Alarm Reg. #1 (51h)

Alarm Reg. #2 (52h)

Alarm Reg. #4 (54h)

Alarm Reg. #3 (53h)

Alarm Reg. #7 (57h)

Alarm Reg. #5 (55h)

Alarm Reg. #6 (56h)

Undefined (58h)

Undefined (59h)

Undefined (5Ah)

Undefined (7Fh)

Undefined (7Dh)

Undefined (7Eh)

Sequence Reg. #0 (48h)

Sequence Reg. #1 (49h)

Sequence Reg. #2 (4Ah)

Sequence Reg. #4 (4Ch)

Sequence Reg. #3 (4Bh)

Sequence Reg. #7 (4Fh)

Sequence Reg. #5 (4Dh)

Sequence Reg. #6 (4Eh)

Temp (00h)

Vccint (01h)

Vccaux (02h)

VP/VN (03h)

Undefined (0Fh)

VAUXP[1]/VAUXN[1] (11h)

V

CCINT

Max (21h)

V

CCAUX

Max (22h)

Undefined (23h)

Temp Max (20h)

V

CCINT

Min (25h)

V

CCAUX

Min (26h)

Undefined (27h)

Temp Min (24h)

VAUXP[0]/VAUXN[0] (10h)

Undefined (0Eh)

Undefined (0Dh)

Control Registers (40h–7Fh)

Read & Write

Read Only

Status Registers (00h–3Fh)

Dynamic Reconfiguration Port - JTAG Arbitrator

Undefined (28h)

Undefined (29h)

Undefined (2Ah)

Flag (3Fh)

Undefined (3Eh)

Undefined (3Dh)

VAUXP[13]/VAUXN[13] (1Dh)

VAUXP[12]/VAUXN[12] (1Ch)

VAUXP[14]/VAUXN[14] (1Eh)

VAUXP[15]/VAUXN[15] (1Fh)

DRP

JTAG TAP

Controller

UG370_07_

060709

www.BDTIC.com/XILINX