16

Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

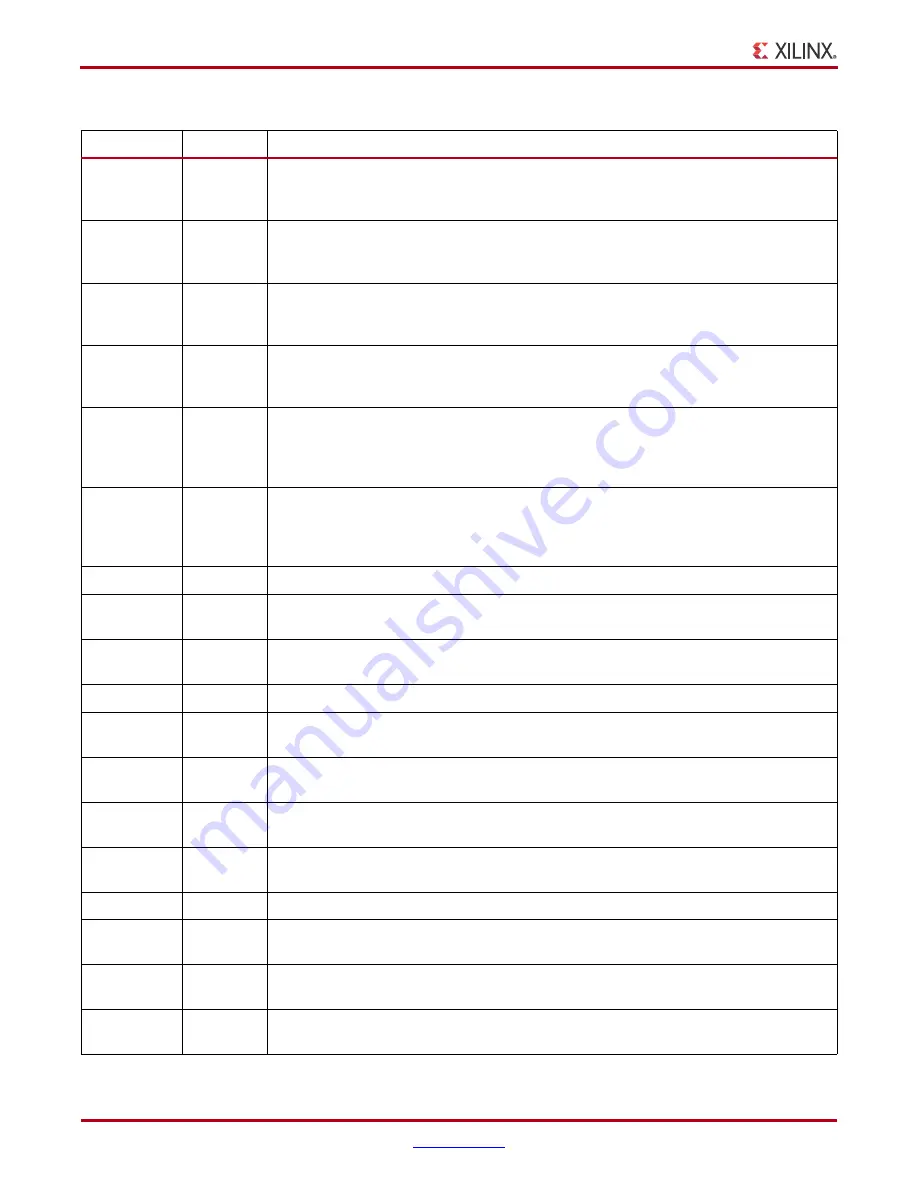

Register File Interface

Table 3:

Status Registers (Read-Only)

Name

Address

Description

Temperature

00h

The result of the on

-chip temperature sensor measurement is stored in this location. The

data is MSB justified in the 16

-bit register. The ten MSBs correspond to the temperature

sensor transfer function shown in

V

CCINT

01h

The result of the on

-chip V

CCINT

supply monitor measurement is stored at this location.

The data is MSB justified in the 16

-bit register. The 10 MSBs correspond to the supply

sensor transfer function shown in

.

V

CCAUX

02h

The result of the on

-chip V

CCAUX

Data supply monitor measurement is stored at this

location. The data is MSB justified in the 16

-bit register. The ten MSBs correspond to the

supply sensor transfer function shown in

V

P

/V

N

03h

The result of a conversion on the dedicated analog input channel is stored in this register.

The ten MSBs correspond to the ADC transfer functions shown in

or

depending on the ADC input configuration.

V

REFP

04h

The result of a conversion on the reference input V

REFP

is stored in this register. The

10 MSBs correspond to the ADC transfer function shown in

. The supply sensor

is used when measuring V

REFP

.This channel is also used during a calibration

(see

V

REFN

05h

The result of a conversion on the reference input V

REFP

is stored in this register. The

10 MSBs correspond to the ADC transfer function shown in

. The supply sensor

is used when measuring V

REFP

. This channel is also used during a calibration

(see

Undefined

06h

to

07h

These locations are unused and contain invalid data.

Supply Offset

08h

The calibration coefficient for the supply sensor offset is stored at this location

(see

ADC Offset

09h

The calibration coefficient for the ADC offset calibration is stored at this location

(see

System Monitor Calibration, page 31

Undefined

0Ah

to

0Fh

These locations are unused and contain invalid data.

V

AUXP

[15:0]/

V

AUXN

[15:0]

10h

to

1Fh

The results of 10

-bit A/D conversions on the auxiliary analog inputs 0 to 15 are stored at

these locations. The data is MSB justified in the 16

-bit register

Max Temp

20h

Maximum temperature measurement recorded since power

-up or the last SYSMON reset.

10

-bit data MSB justified.

Max V

CCINT

21h

Maximum V

CCINT

measurement recorded since power

-up or the last SYSMON reset.

10

-bit data MSB justified.

Max V

CCAUX

22h

Maximum V

CCAUX

measurement recorded since power

-up or the last SYSMON reset.

10

-bit data MSB justified.

Undefined

23h

This location contains invalid data.

Min Temp

24h

Minimum temperature measurement recorded since power

-up or the SYSMON reset.

10

-bit data MSB justified.

Min V

CCINT

25h

Minimum V

CCINT

measurement recorded since power

-up or the last SYSMON reset.

10

-bit data MSB justified.

Min V

CCAUX

26h

Minimum V

CCAUX

measurement recorded since power

-up or the last SYSMON reset.

10

-bit data MSB justified.

www.BDTIC.com/XILINX