Virtex-6 FPGA System Monitor

35

UG370 (v1.1) June 14, 2010

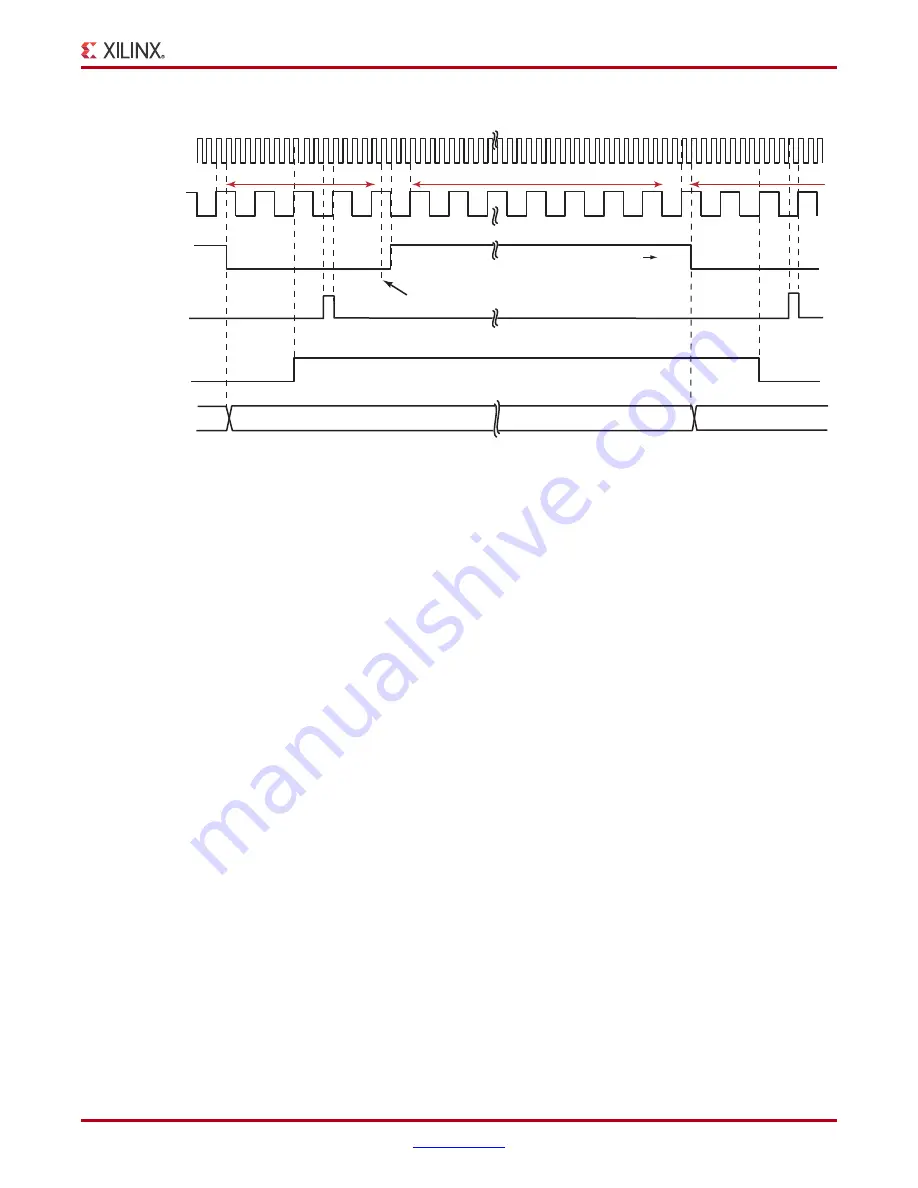

System Monitor Timing

Conversion Phase

The conversion phase starts on the sampling edge (next rising edge of DCLK) at the end of

the acquisition phase. The BUSY signal transitions to an active High on the next rising edge

of DCLK to indicate the ADC is carrying out a conversion. The conversion phase is 22

ADCCLK cycles. The conversion result transfers to the status registers 10 DCLK cycles

after BUSY transitions Low, and the EOC logic output pulses High for one DCLK cycle. If

the channel being converted is also being filtered, then the filtered data is only transferred

to the status registers when the last sample result has been converted. Thus, if a channel is

being averaged, an EOC pulse is only generated for the last conversion result, such as the

16

th

, 64

th

, 256

th

sample (see

). When

averaging is enabled, write operations to the configuration registers will not be acted on

until EOC is pulsed, i.e., when the filtering operation is complete.

When System Monitor is being operated in sequence mode, the user identifies the channel

being converted by monitoring the channel address (CHANNEL[4:0]) logic outputs. The

multiplexer channel address of the channel being converted is updated on these logic

outputs when BUSY transitions Low at the end of the conversion phase. The channel

address outputs can be used with the EOC and DRDY signals to automatically latch the

contents of the output data registers into a FIFO or block RAM (see

). This is accomplished by connecting the CHANNEL[4:0] outputs to

DADDR[4:0] (with DADDR[6:5] = 0), using EOC as a DEN (enable) for the DRP, and using

DRDY as a WE (write enable) for the block RAM.

System Monitor’s EOS signal has the same timing as EOC. This signal is pulsed when the

output data register for the last channel in a programmed channel sequence is updated.

X-Ref Target - Figure 14

Figure 14:

Continuous Sampling Mode Timing

DCLK

1

104

1

9

18

12

19

2

3

4

10

6

12

7

13

26

31

5

11

25

30

1

2

3

4

32

24

23

29

ADCCLK

Acquisition cycles can be extended to 10 to allow more acquisition time

Acquisition Time

Acquisition Time

Conversion Time

BUSY

Nth Conversion Finished

Nth Sampling Edge

EOC / EOS

ALM[2:0] / OT

CHANNEL[4:0]

N-1 Channel Selection

N Selection

UG370_14_060809

www.BDTIC.com/XILINX