Virtex-6 FPGA System Monitor

39

UG370 (v1.1) June 14, 2010

Analog Inputs

Analog Inputs

The analog inputs of the ADC use a differential sampling scheme to reduce the effects of

common-mode noise signals. This common-mode rejection improves the ADC

performance in noisy digital environments.

shows the benefits of a differential

sampling scheme. Common ground impedances (R

G

) easily couple noise voltages

(switching digital currents) into other parts of a system. These noise signals can be 100 mV

or more. For the System Monitor ADC, this noise voltage is equivalent to 100 LSBs, thus

inducing large measurement errors. The differential sampling scheme samples both the

signal and any common mode noise voltages at both analog inputs (V

P

and V

N

). The

common mode signal is effectively subtracted because the Track-and-Hold amplifier

captures the difference between V

P

and V

N

, such as, V

P

– V

N

(see

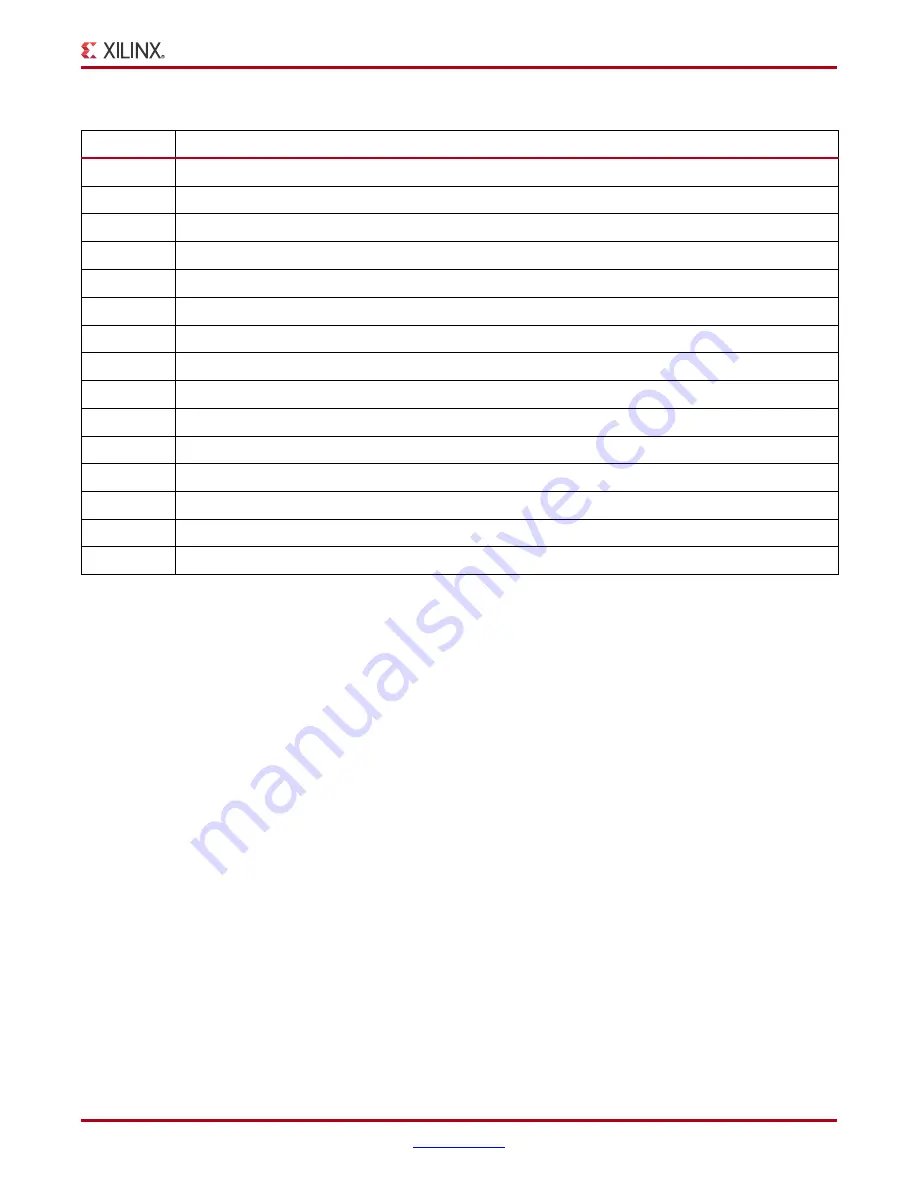

Table 19:

Timing Event Information

Event

Description

t

1

DCLK period

(1)

t

2

Minimum DEN setup time before the rising edge of DCLK

(2)

t

3

Minimum DEN hold time after the falling edge of DCLK

t

4

Minimum DWE setup time before the rising edge of DCLK

(3)

t

5

Minimum DWE hold time after the falling edge of DCLK

(3)

t

6

Minimum DRP address set up time before rising edge of DCLK

t

7

Minimum DRP address hold time after rising edge of DCLK

t

8

Minimum DRP input data bus set up time before rising edge of DCLK

t

9

Minimum DRP input data bus hold time after rising edge of DCLK

t

10

Maximum DRP DCLK to DO delay/access time

(4)

t

11

Maximum delay on DRDY going High/Low after a rising edge on DCLK

t

12

Maximum delay on EOC/EOS going High/Low after a rising edge on DCLK

t

13

Maximum delay on ALM[2:0]/OT going High after a rising edge on DCLK

t

14

Maximum delay on BUSY going High/Low after a rising edge on DCLK

t

15

Maximum delay on CHANNEL[4:0] on rising edge of DCLK

Notes:

1. Minimum DCLK duty cycle is 60/40.

2. DEN should

only

be pulsed for one DCLK cycle.

3. For a DRP write operation, address on DADDR[6:0] and DI[15:0] are latched on the rising edge of DCLK when DEN and WEN are

High. The data is in placed in the DRP register three DCLK cycles later. DRDY goes High when the data has been written. See the

Dynamic Reconfiguration Port description in the

Virtex-6 FPGA Configuration Guide

for more information.

4. For a DRP read operation, address on DADDR[6:0] is latched on the rising edge of DCLK when DEN is High, and three DCLK cycles

later the data is placed on the DO bus. DRDY goes High when the data on DO is valid. See the Dynamic Reconfiguration Port

description in the

Virtex-6 FPGA Configuration Guide

for more information.

www.BDTIC.com/XILINX