ADM-PCIE-8K5-FH User Manual

•

set_property CONFIG_MODE {BPI16} [current_design]

•

set_property CFGBVS GND [ current_design ]

•

set_property CONFIG_VOLTAGE 1.8 [ current_design ]

Generate an MCS file with these properties (write_cfgmem):

•

-format MCS

•

-size 128

•

-interface BPIx16

•

-loadbit "up 0x0000000 <directory/to/file/filename.bit>" (failsafe location)

•

-loadbit "up 0x2000000 <directory/to/file/filename.bit>" (default location)

Program with vivado hardware manager with these settings:

•

BPI part number: mt28gu01gaax1e-bpi-x16

•

State of non-config mem I/O pins: Pull-none

•

RS bits: 25:24

3.10.1.2 Custom Flash Write Interface

Alpha Data's reference design bridge allows users to write images to the BPI configuration flash over the PCIE

interface. Other customers may want similar functionality built into their own IP. In order to enable this

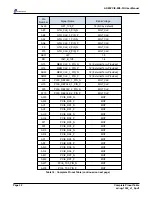

functionality, users must reference the FLASH* pins in

Complete Pinout Table

and utilize the STARTUPE3

primitive to control certain dedicated configuration pins (i.e. D0-D3). Complete details on the STARTUPE3

primitive can be found in Xilinx UG570.

3.10.2 Configuration via JTAG

A micro-USB AB Cable may be attached to the lower front panel USB port. This permits the FPGA to be

reconfigured using the Xilinx Vivado Hardware Manager via the integrated Digilent JTAG converter module.

Page 17

Functional Description

ad-ug-1342_v1_0.pdf