B1.21

AArch32 Virtual memory control registers

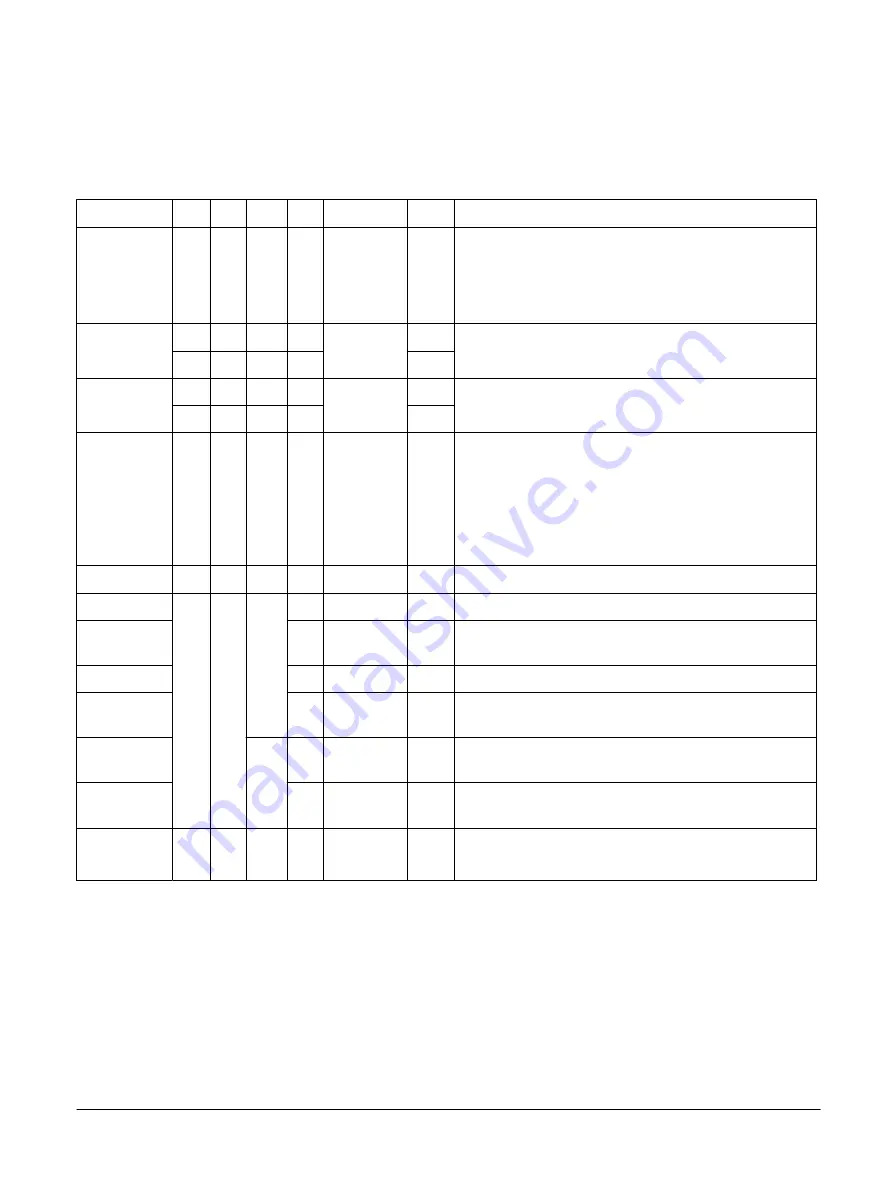

The following table shows the virtual memory control registers.

Table B1-20 Virtual memory control registers

Name

CRn Op1 CRm Op2 Reset

Width Description

SCTLR

c1

0

c0

0

0x00C50838

32-bit

B1.105 System Control Register

The reset value depends on inputs,

CFGTE

,

CFGEND

, and

VINITHI

. The value listed here assumes these signals are set to

LOW.

TTBR0

c2

0

c0

0

UNK

32-bit Translation Table Base Register 0, see

-

0

c2

-

64-bit

TTBR1

c2

0

c0

1

UNK

32-bit Translation Table Base Register 1, see

-

1

c2

-

64-bit

TTBCR

c2

0

c0

2

0x00000000

32-bit

B1.110 Translation Table Base Control Register

The reset value is

0x00000000

for the Secure copy of the

register. The reset value for the EAE bit of the Non-secure copy

of the register is

0x0

. You must program the Non-secure copy of

the register with the required initial value, as part of the

processor boot sequence.

DACR

c3

0

c0

0

UNK

32-bit

B1.47 Domain Access Control Register

PRRR

c10

0

c2

0

UNK

32-bit

B1.101 Primary Region Remap Register

MAIR0

0

UNK

32-bit

B1.95 Memory Attribute Indirection Registers 0 and 1

NMRR

1

UNK

32-bit

B1.99 Normal Memory Remap Register

MAIR1

1

UNK

32-bit

B1.95 Memory Attribute Indirection Registers 0 and 1

AMAIR0

c3

0

0x00000000

32-bit

B1.36 Auxiliary Memory Attribute Indirection Register 0

AMAIR1

1

0x00000000

32-bit

B1.37 Auxiliary Memory Attribute Indirection Register 1

CONTEXTIDR c13

0

c0

1

UNK

32-bit Process ID Register, see the

Arm

®

Architecture Reference

Manual Armv8, for Armv8-A architecture profile

B1 AArch32 system registers

B1.21 AArch32 Virtual memory control registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B1-178

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......