B2.2

AArch64 Identification registers

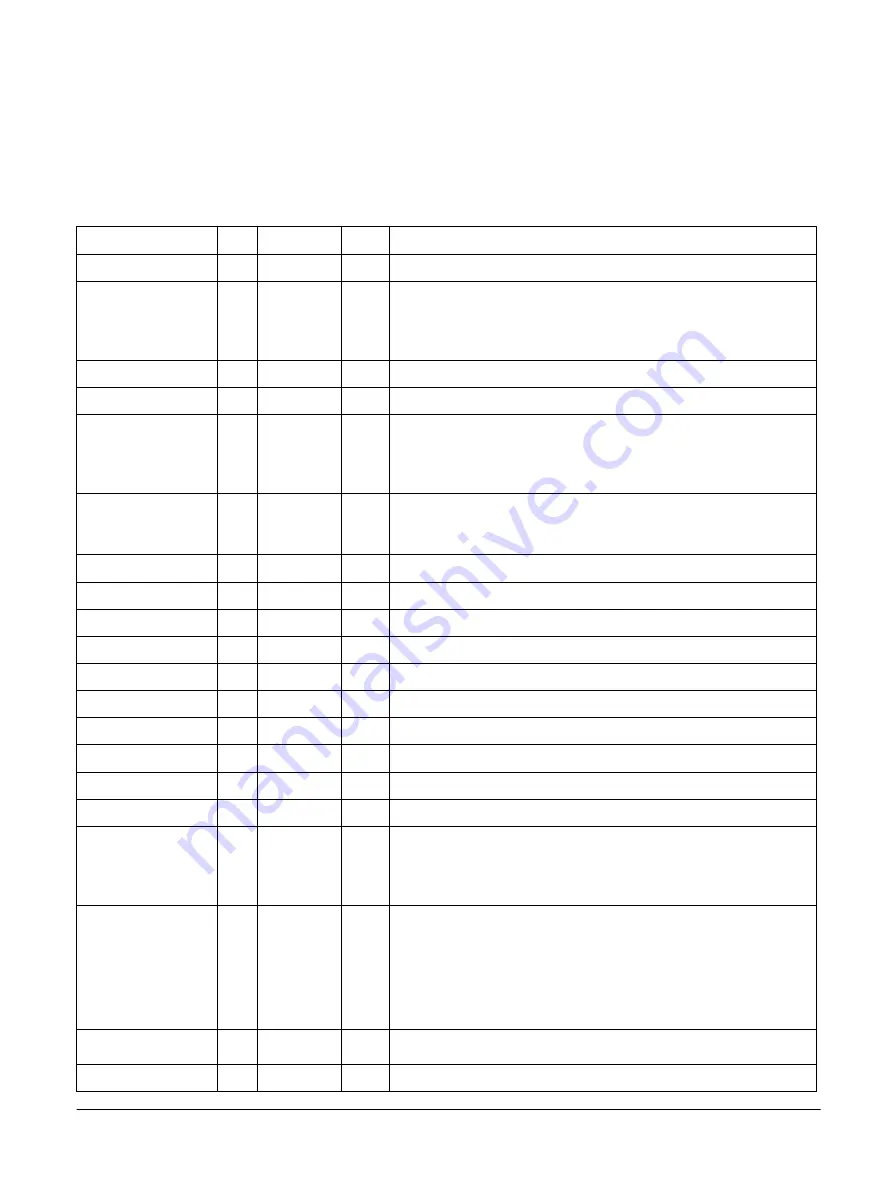

The following table shows the identification registers in AArch64 state.

Bits[63:32] are reset to

0x00000000

for all 64-bit registers in the table.

Table B2-1 AArch64 identification registers

Name

Type Reset

Width Description

MIDR_EL1

RO

0x411FD040

32

MPIDR_EL1

RO

-

64

B2.84 Multiprocessor Affinity Register, EL1

The reset value depends on the primary inputs,

CLUSTERIDAFF1

and

CLUSTERIDAFF2

, and the number of cores that the device implements.

REVIDR_EL1

RO

0x00000000

32

B2.86 Revision ID Register, EL1

ID_PFR0_EL1

RO

0x00000131

32

B2.67 AArch32 Processor Feature Register 0, EL1

ID_PFR1_EL1

RO

0x10011011

32

B2.68 AArch32 Processor Feature Register 1, EL1

Bits [31:28] are

0x1

if the GIC CPU interface is present and enabled,

and

0x0

otherwise.

ID_DFR0_EL1

RO

0x03010066

32

B2.56 AArch32 Debug Feature Register 0, EL1

Bits [19:16] are

0x1

if ETM is implemented, and

0x0

otherwise.

ID_AFR0_EL1

RO

0x00000000

32

B2.55 AArch32 Auxiliary Feature Register 0, EL1

ID_MMFR0_EL1

RO

0x10201105

32

B2.63 AArch32 Memory Model Feature Register 0, EL1

ID_MMFR1_EL1

RO

0x40000000

32

B2.64 AArch32 Memory Model Feature Register 1, EL1

ID_MMFR2_EL1

RO

0x01260000

32

B2.65 AArch32 Memory Model Feature Register 2, EL1

ID_MMFR3_EL1

RO

0x02102211

32

B2.66 AArch32 Memory Model Feature Register 3, EL1

ID_ISAR0_EL1

RO

0x02101110

32

B2.57 AArch32 Instruction Set Attribute Register 0, EL1

ID_ISAR1_EL1

RO

0x13112111

32

B2.58 AArch32 Instruction Set Attribute Register 1, EL1

ID_ISAR2_EL1

RO

0x21232042

32

B2.59 AArch32 Instruction Set Attribute Register 2, EL1

ID_ISAR3_EL1

RO

0x01112131

32

B2.60 AArch32 Instruction Set Attribute Register 3, EL1

ID_ISAR4_EL1

RO

0x00011142

32

B2.61 AArch32 Instruction Set Attribute Register 4, EL1

ID_ISAR5_EL1

RO

0x00011121

32

B2.62 AArch32 Instruction Set Attribute Register 5, EL1

ID_ISAR5_EL1 has the value

0x00010001

if the Cryptographic Extension

is not implemented and enabled.

ID_AA64PFR0_EL1

RO

0x01002222

64

B2.54 AArch64 Processor Feature Register 0, EL1

Bits [27:24] are

0x1

if the GIC CPU interface is present and enabled,

and

0x0

otherwise.

Bits [23:16] are

0x00

if the Advanced SIMD and floating-point support is

implemented, and

0xFF

otherwise.

ID_AA64PFR1_EL1

RO

0x00000000

64

AArch64 Processor Feature Register 1

ID_AA64DFR0_EL1

RO

0x10305106

64

B2.51 AArch64 Debug Feature Register 0, EL1

B2 AArch64 system registers

B2.2 AArch64 Identification registers

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

B2-363

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......