A2.4

About the Generic Timer

The Generic Timer can schedule events and trigger interrupts that are based on an incrementing counter

value. It generates timer events as active-LOW interrupt outputs and event streams.

The Cortex

‑

A35 processor does not include the system counter. This resides in the SoC. The system

counter value is distributed to the Cortex

‑

A35 processor with a synchronous binary encoded 64-bit bus,

CNTVALUEB[63:0]

.

Because

CNTVALUEB[63:0]

is generated from a system counter that typically operates at a slower

frequency than the processor clock,

CLKIN

, the

CNTCLKEN

input is provided.

CNTCLKEN

is

registered inside the processor and then used as a clock enable for

CNTVALUEB[63:0]

. This allows a

multicycle path to be applied to the

CNTVALUEB[63:0]

. The following figure shows the interface.

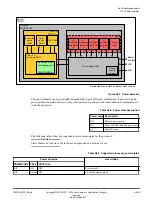

Processor

Clock gate

CNTCLKEN

register

Architectural

counter

registers

CNTVALUEB[63:0]

CNTCLKEN

Figure A2-3 Generic Timer interface

The value on

CNTVALUEB[63:0]

is required to be stable whenever the internally registered version of

the

CNTCLKEN

clock enable is asserted.

CNTCLKEN

must be synchronous and balanced with

respect to

CLKIN

and must toggle at integer ratios of the processor

CLKIN

.

Related information

A.6 Generic Timer signals

on page Appx-A-855

A2 Technical Overview

A2.4 About the Generic Timer

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A2-47

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......