B.1

Revisions

This appendix describes the technical changes between released issues of this book

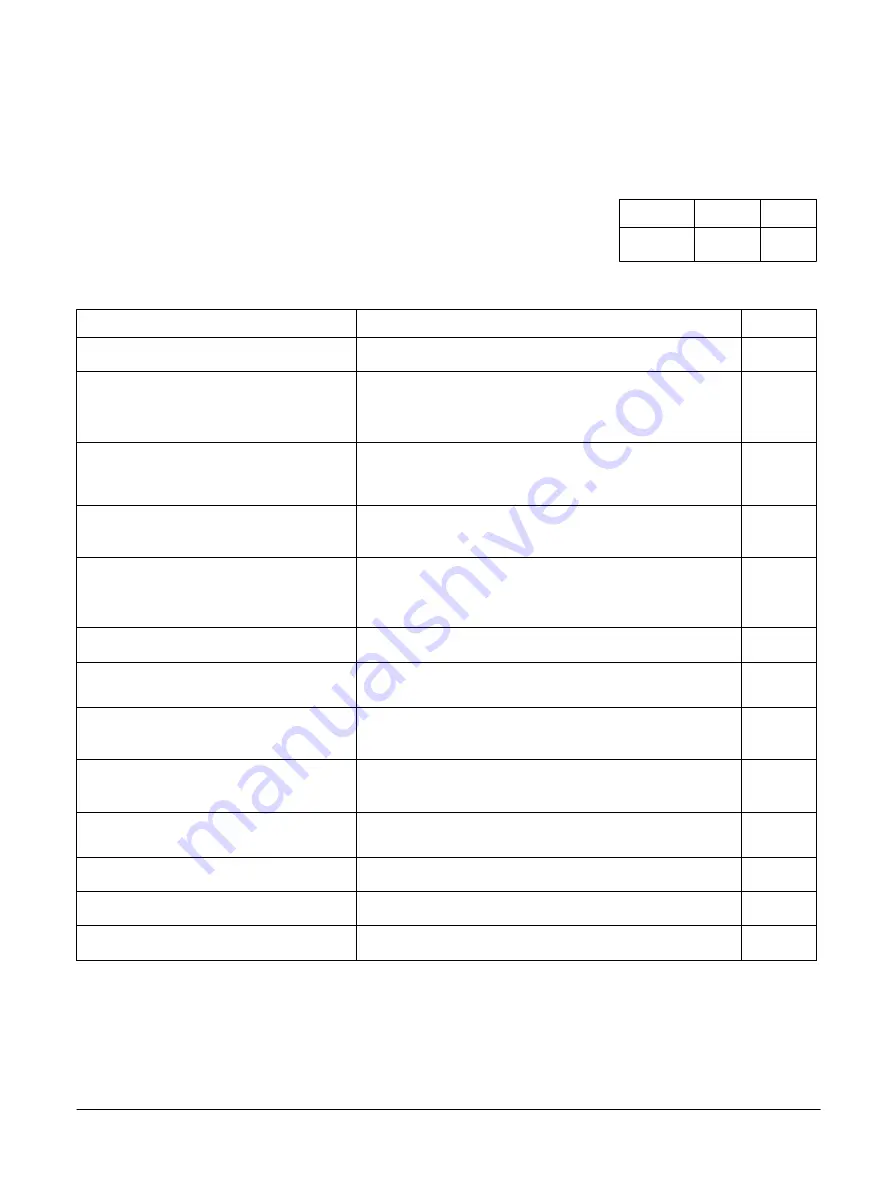

Table B-1 Issue 0000-00

Change

Location Affects

First release -

-

Table B-2 Differences between Issue 0000-00 and Issue 0100-00

Change

Location

Affects

Added support for 128KB L2 cache size.

Throughout document

r1p0

Added note to indicate support for Dot Product

instructions introduced in the Armv8.4

Extension.

r1p0

Updated BPIQ data location encoding table.

r1p0

Updated replacement policy to dynamic biased

replacement policy.

A7.1 About the L2 memory system

r1p0

Updated reset values for ID_AA64ISAR0_EL1,

IDAA64MMFR1_EL1, IDMMFR4_EL1, and

MIDR_EL1.

B2.4 AArch64 registers by functional group

r1p0

Updated CCSIDR_EL1 encodings table.

B2.18 CCSIDR_EL1, Cache Size ID Register, EL1

r1p0

Updated CPUECTLR_EL1 register description.

B2.26 CPUECTLR_EL1, CPU Extended Control Register, EL1

r1p0

Updated bits [43:32] of ID_AA64ISAR0_EL1

register.

B2.56 ID_AA64ISAR0_EL1, AArch64 Instruction Set Attribute

Register 0, EL1

r1p0

Updated bits [15:12] of ID_AA64MMFR1_EL1

register.

B2.59 ID_AA64MMFR1_EL1, AArch64 Memory Model Feature

Register 1, EL1

r1p0

Added ID_ISAR6_EL1 register.

B2.71 ID_ISAR6_EL1, AArch32 Instruction Set Attribute Register 6,

EL1

r1p0

Added Activity Monitor Unit chapter.

Chapter C3 Activity Monitor Unit

All versions

Updated reset value for TRCIDR1 register.

r1p0

Updated bits [3:0] of TRCIDR1 register.

r1p0

B Revisions

B.1 Revisions

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

Appx-B-600

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......