CS5374

CS5374

25

5.5 Example: CS5374 Configuration by the CS5376A SPI 2 Port

The CS5374 SPI port was designed to connect to

the CS5376A secondary SPI 2 port as shown in

Figure 12 on page 15.

The CS5376A SPI 2 hardware is controlled by

writing internal digital filter registers SPI2CTRL,

SPI2CMD, and SPI2DAT through a primary SPI 1

port. Chip selects are enabled by writing the

GPCFG0 digital filter register prior to initiating

SPI 2 transactions.

Configuring CS5374 using SPI 2 is more complex

than using an external SPI master, but has the ad-

vantage of a single standardized hardware interface

(the primary SPI 1 port on CS5376A) to control

the entire chipset.

5.5.1 CS5376A SPI 1 Transactions

The CS5376A primary SPI 1 port is controlled by

an external SPI master writing commands and data

into the SPI 1 registers (SPICMD, SPIDAT1, and

SPIDAT2). Serial transactions into the CS5376A

primary SPI 1 port start with an SPI opcode, fol-

lowed by an SPI address, and then data bytes writ-

ten starting at that SPI address. These data bytes

contain internal commands to write the CS5376A

digital filter registers that control the SPI 2 hard-

ware and enable the chip selects.

A full description of how to write the CS5376A in-

ternal digital filter registers using the primary SPI 1

port is described in the CS5376A data sheet.

GPIO Register

Certain GPIO pins on the CS5376A have dual-use

as chip selects for the SPI 2 port. The GPIO0:CS0

and GPIO1:CS1 pins are recommended as dedicat-

ed chip selects when connecting two CS5374 de-

vices to the CS5376A SPI 2 port. To operate the

CS0 and CS1 pins as SPI 2 chip selects they must

be programmed as outputs in the GPCFG0 digital

filter register, as shown in Table 5.

SPI2 Registers

Three digital filter registers control the CS5376A

SPI 2 hardware. The SPI2CMD register is 16-bits

wide and contains the first two bytes of the SPI 2

transaction, the SPI opcode and SPI address, in the

lower two bytes (i.e. 0x000204).

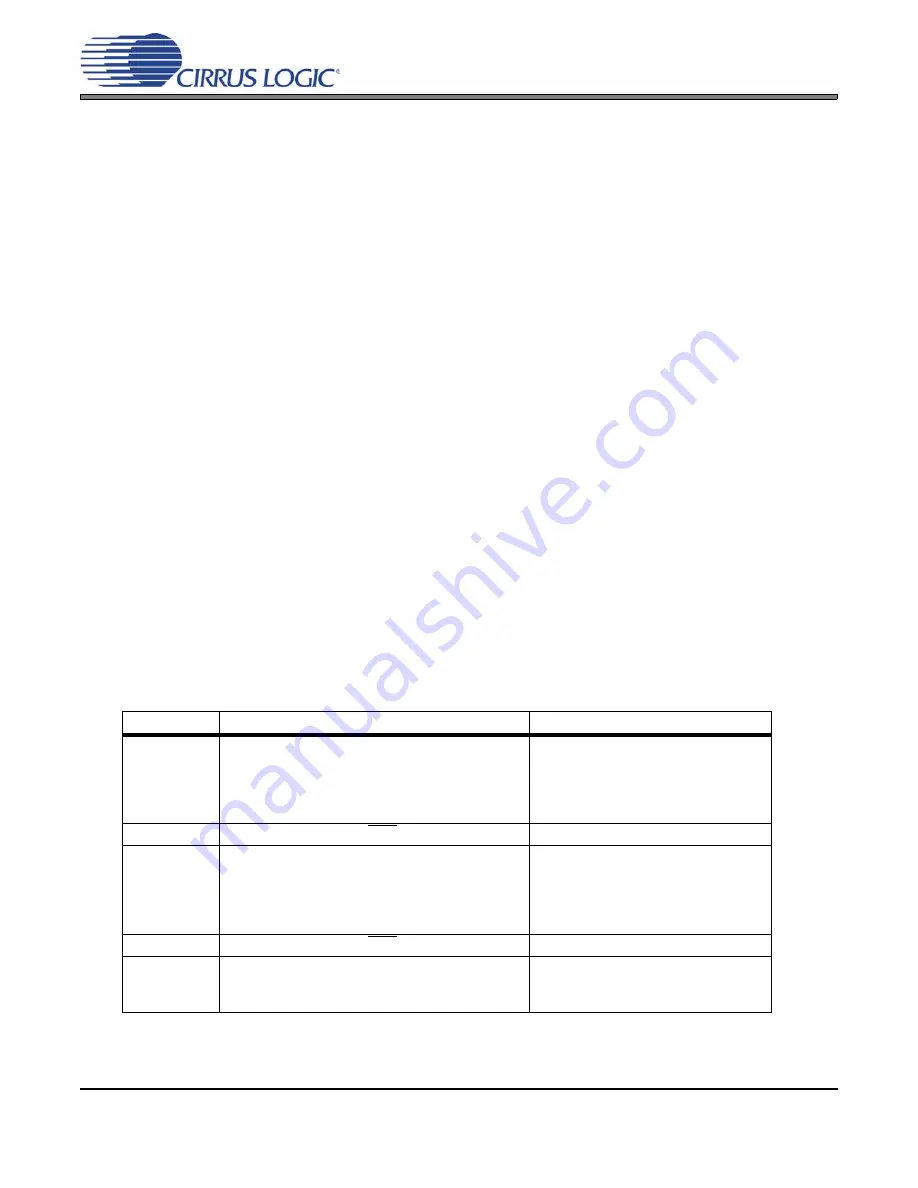

Table 5. Example CS5376A SPI 1 Transactions to Write and Read the GPCFG0 Register

Transaction

CS5376A Primary SPI 1 Write

Description

01

MOSI: 02 | 03 | 00 00 01 | 00 00 0E | 03 FF FF

MISO: -----------------------------------------------------------

SPI Command : 0x02 : Write

SPI Address : 0x03 : SPICMD

SPICMD : 0x000001 : Write Register

SPIDAT1 : 0x00000E : GPCFG0

SPIDAT2 : 0x03FFFF : CS as Output

02

Delay 1ms, monitor SINT, or poll E2DREQ

See the CS5376A data sheet.

03

MOSI: 02 | 03 | 00 00 02 | 00 00 0E | 00 00 00

MISO: -----------------------------------------------------------

SPI Command : 0x02 : Write

SPI Address : 0x03 : SPICMD

SPICMD : 0x000002: Read Register

SPIDAT1 : 0x00000E : GPCFG0

SPIDAT2 : 0x000000 : Dummy

04

Delay 1ms, monitor SINT, or poll E2DREQ

See the CS5376A data sheet.

05

MOSI: 03 | 06 |---------------|

MISO: -------------| 03 FF FF |

SPI Command : 0x03 : Read

SPI Address : 0x06 : SPIDAT1

SPIDAT1 : 0x03FFFF : GPCFG0