ATHENA :

Embedded

Vortex

86

AIO SBC

21

2.8 Watchdog

Timer

The watchdog timer work flow of Vortex86 is: If the watchdog timer expires the first time, the

expired event will set SFTMR0_STS and timer will reload its inital value and count again. If the

timer expire the second time, the expired event will set SFTMR1_STS.

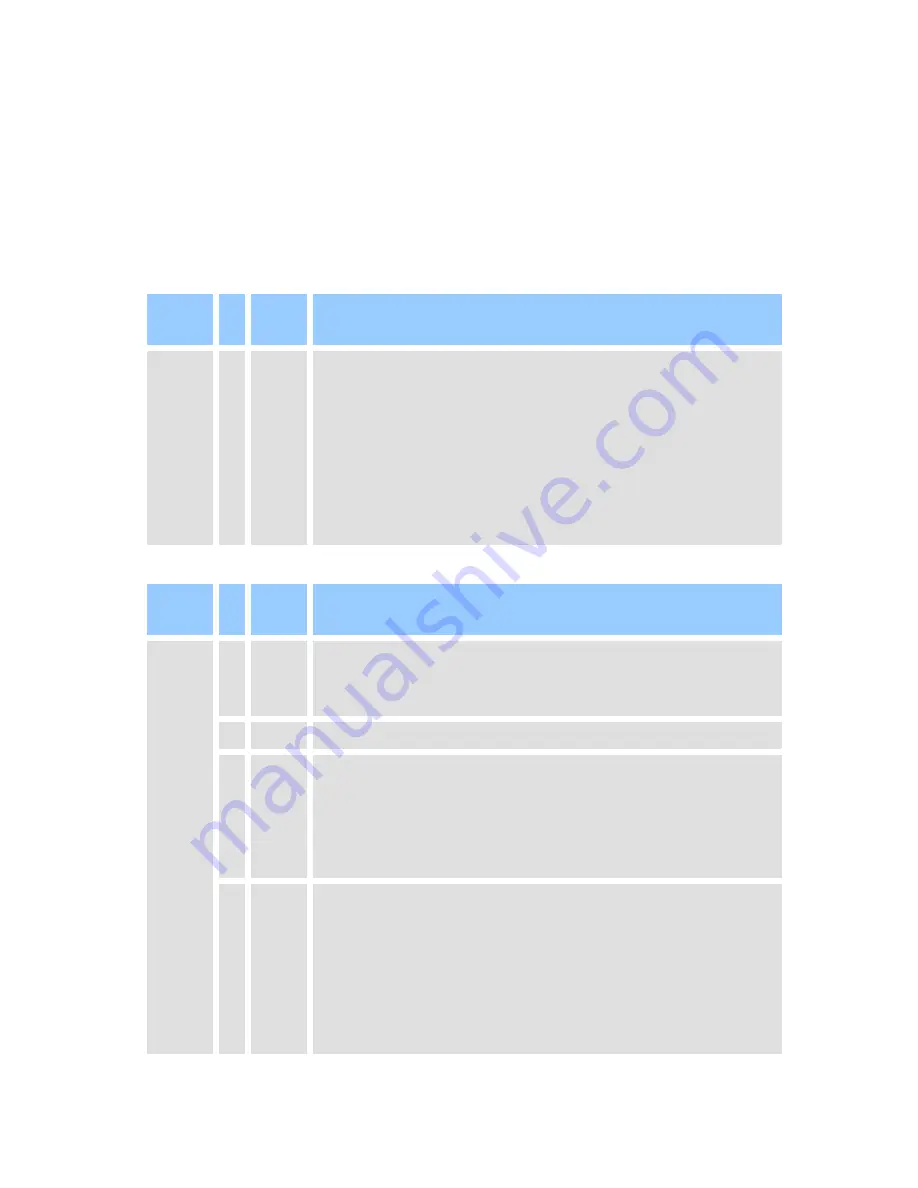

Software Watchdog Timer Initial Value:

Default Value: FFh

I/O

Address

Bit Access Description

84Ah

7:0 R/W

Software Watchdog Timer Initial Value

Writing to this register will reload the software watchdog timer

with the value specified in this register. If the software watchdog

timer expires the first time, the expired event will set the

SFTMR0_STS and the timer will reload its initial value and

count again. If the timer expire the second time, the expired

event will set the SFTMR1_STS. The timer value can't be read

from this field.

Software Watchdog Timer Control Register:

Default Value: 00h

I/O

Address

Bit Access Description

7 R/W

Software Watchdog Timer Counting Enable

The software watchdog timer will start to count when this bit is

set to one.

6 RO

Reserved

5:4 R/W

Software Watchdog Timer Clock Select

00 : 4 ms

01 : 1 second

10 : 1 minute

11 : 1 hour

84Bh

3:2 R/W

Software Watchdog Timer Expiration Event 1 Routing Select

When SFTMR1_STS is set to one, an SMI#/SFTIRQ/PCIRST#

will be generated according to the following combination.

00 : No effect

01 : SMI#

10 : SFTIRQ

11 : PCIRST#