2. PCI Interface

50

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

2.3.3

Data Phase

The data phase deals with the control of burst length.

2.3.3.1

Writes

For non-DMA writes, the length of the PCI write transaction is dependent on the length of the

transaction delivered from the source bus. Writes originating from the processor bus can be either

single cycle writes or burst writes. Burst writes from the processor bus are always 32 bytes in length.

This burst is converted to an 8 byte burst on a 32-bit PCI bus. Either PCI-1 or PCI-2 can be configured

as 32-bit. Single cycle writes from the 64-bit processor bus are translated into two 8 byte burst writes

on the 32-bit PCI bus. This information is summarized in

The PB Master can also generate extended cycles. Extended cycles are either 16 byte or 24 byte

transactions. These cycles are enabled by setting the Extended Cycle (EXTCYC) bit to 1 in the

“Processor Bus Miscellaneous Control and Status Register” on page 304

When the Dual PCI PowerSpan II is used, incoming PCI writes are executed as similar writes on the

alternate PCI interface. For example, a 64-byte burst write to memory space from the PCI-1bus is

executed as a 64-byte burst write to the memory space on the PCI-2 bus, provided the target on PCI-2

does not disconnect.

DMA Writes

The PowerSpan II DMA channels always attempt to perform the longest possible burst

—

up to

128-bytes

—

on the PCI bus.

2.3.3.2

Reads

The minimum memory read prefetch quantity is 8 bytes (default). Setting the MEM_IO bit in the

“PCI-1 Target Image x Control Register” on page 268

enables 1,2,3, or 4 byte memory reads on the

PCI bus.

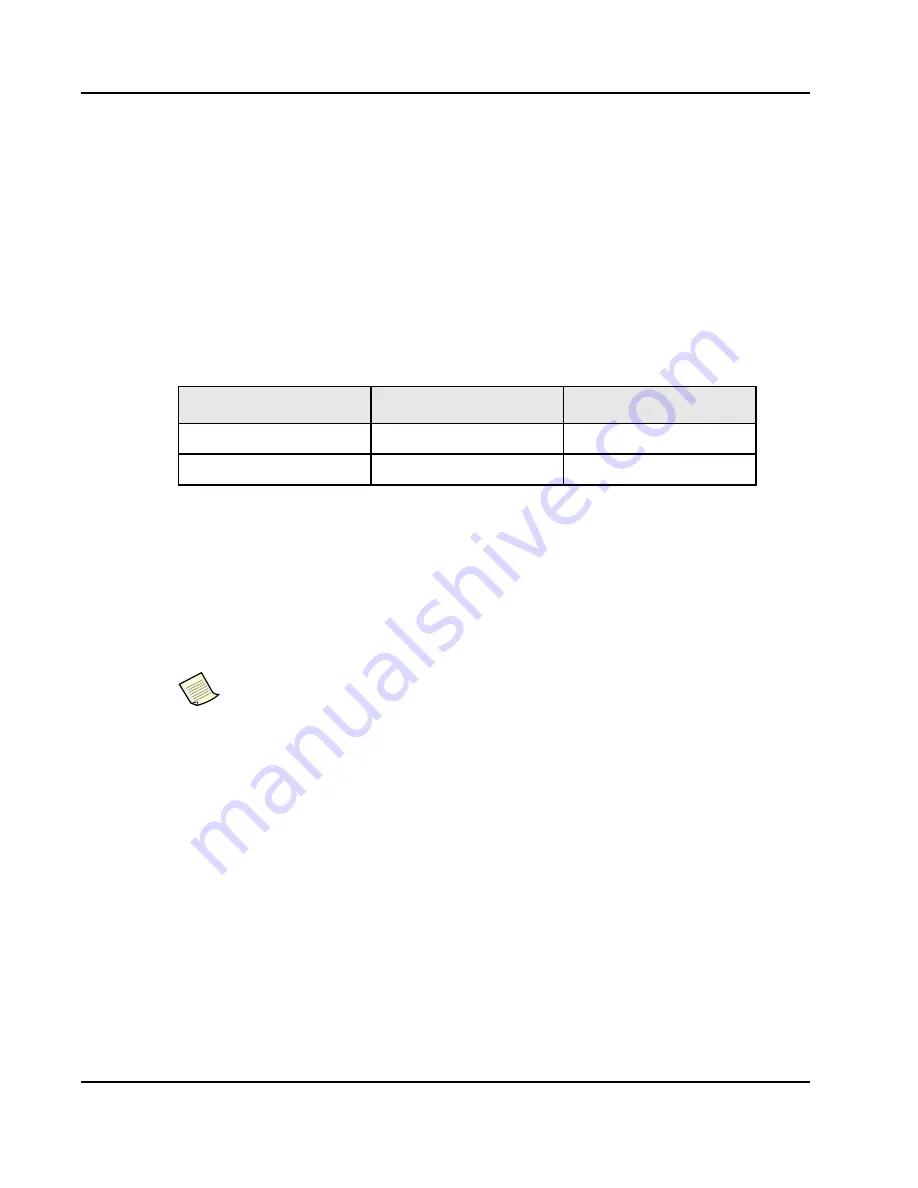

Table 8: PB Writes and Their Corresponding PCI Writes

PB Write

64-bit PCI Write

32-bit PCI Write

32-byte Line Write

4-beat 32-byte Burst Write

8-beat 32-byte Burst Write

8-byte Single Write

Single Beat 8-byte Write

2-beat 8-byte Burst Write

Write transactions intended for I/O space on the alternate PCI bus must be single

beat writes. Bursting is not supported for a target image programmed to generate

an I/O access on the alternate PCI bus. A burst write directed at such a target

image results in a Target-Disconnect after every data beat.