7

µFlashTCP-EP

User’s Manual

JK

microsystems

COM1 is wired as Data Terminal Equipment (DTE) for connection to a peripheral such as a

modem. This is a full function RS-232 port implementing all of the handshaking and control

lines with the exception of the Ring Indicator input. The UART base address is at I/O location

3F8h and can be configured to use IRQ 4.

COM2 is the default console and is wired as Data Communications Equipment (DCE) for direct

connection to a computer or terminal. This port is software configurable as a 3 wire RS-232 port

implementing RxD and TxD or as a half duplex RS-485 port. The UART base address is at I/O

location 2F8h and can be configured to use IRQ 3.

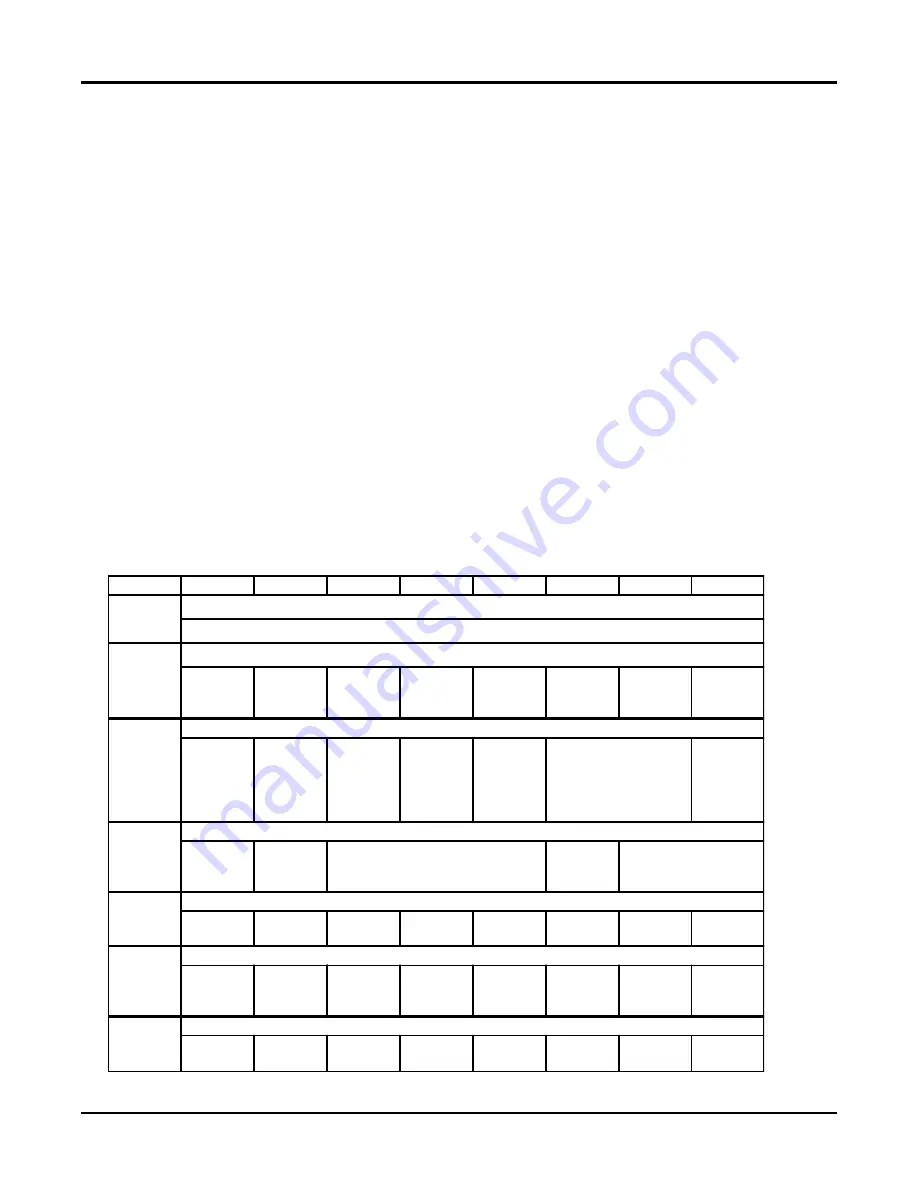

The following table shows the UART configuration and control registers. Please refer to the Intel

386Ex data sheet for more information on the serial ports and their configuration.

The DATA and IER registers also hold the baud rate divisor. When the high bit of the LCR

(DLA) is set, the divisor value can be written to DATA and IER. DATA contains the low byte and

IER contains the high byte. To determine the required divisor, divide 115200 by the required

baud rate. Program the divisor with the nearest integer value. When access to the divisor value

is no longer required, clear the DLA bit.

7

6

5

4

3

2

1

0

Base

Receive/Transmit Holding Register / Divisor Latch Low (DATA)

Data In, Data Out

Base+1

Interrupt Enable Register (IER)

0

0

0

0

Modem

Status

Receive

Line Status

Transmit

Buffer

Empty

Receive

Buffer

Full

Base+2

Interrupt Identification Register / Divisor Latch High (IIR)

Reserved

Reserved

Reserved

Reserved

Reserved

Interrupt Source

00=Modem Status

01=Transmit Buffer Empty

10=Receive Buffer Full

11=Receiver Line Status

Interrupt

Pending

(0=Pending)

Base+3

Line Control Register (LCR)

Divisor

Latch

Access

Send Break

Parity

000=None, 001= Odd, 011=Even,

101=Mark, 111=Space

Stop Bits,

0=1, 1=2

Word Length, 00=5,

01=6,

10=7, 11=8

Base+4

Modem Control Register (MCR)

0

0

0

Loop Back

Test

Ext. Int.

Enable

Out1

RTS

DTR

Base+5

Line Status Register (LSR)

Reserved

Transmit

Register

Empty

Transmit

Buffer

Empty

Break

Interrupt

Framing

Error

Parity Error Overrun

Error

Receive

Buffer Full

Base+6

Modem Status Register (MSR)

DCD

RI

DSR

CTS

∆

DCD

∆

RI

∆

DSR

∆

CTS

Table 1: UART Registers

Hardware

Summary of Contents for 89-0040

Page 1: ...µFlashTCP EP User s Manual ...

Page 2: ......