2-Port USB 2.0 Hi-Speed Hub Controller

Datasheet

DS00001726A-page 38

2014 Microchip Technology Inc.

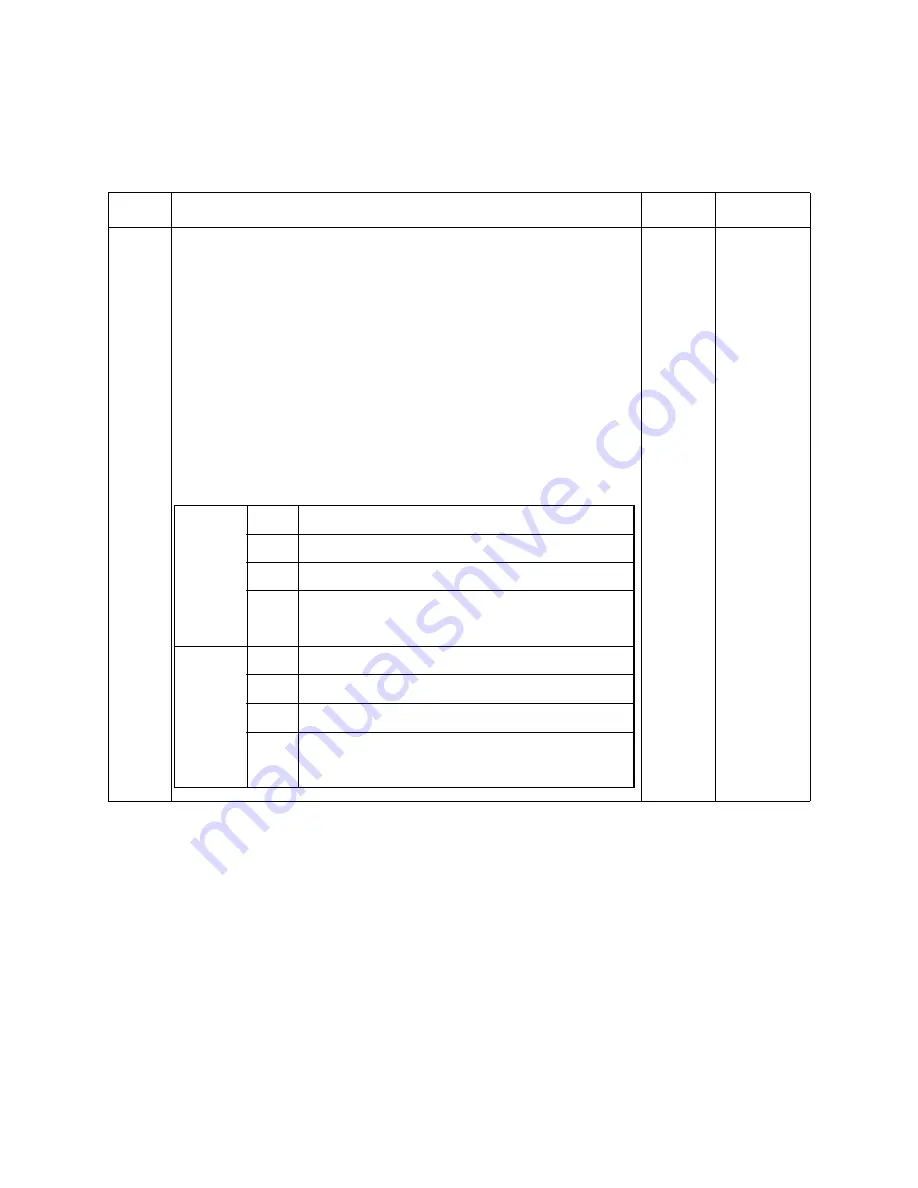

4.4.30

Port 1/2 Remap Register (PRTR12)

Address:

Size:

8 bits

BITS

DESCRIPTION

TYPE

DEFAULT

7:0

Port 1/2 Remap (PRTR12)

When a hub is enumerated by a USB Host Controller, the hub is only

permitted to report how many ports it has, the hub is not permitted to select

a numerical range or assignment. The Host Controller will number the

downstream ports of the hub starting with the number '1', up to the number

of ports that the hub reported as having.

The host's port number is referred to as “Logical Port Number” and the

physical port on the hub is the “Physical Port Number”. When remapping

mode is enabled (PRTMAP_EN in the

Configuration Data Byte 3 Register

), the hub's downstream port numbers can be remapped to different

logical port numbers assigned by the host.

Note:

The OEM must ensure that Contiguous Logical Port Numbers are

used, starting from one up to the maximum number of enabled

ports. This ensures that the hub's ports are numbered in

accordance with the way a Host will communicate with the ports.

R/W

00h

Bits[7:4] =

0000

Physical Port 2 is disabled

0001

Physical Port 2 is mapped to Logical Port 1

0010

Physical Port 2 is mapped to Logical Port 2

0011

to

1111

RESERVED

Will default to 0000 value.

Bits[3:0] =

0000

Physical Port 1 is disabled

0001

Physical Port 1 is mapped to Logical Port 1

0010

Physical Port 1 is mapped to Logical Port 2

0011

to

1111

RESERVED

Will default to 0000 value.