IGLOO2 FPGA Adaptive FIR Filter Demo Guide

Revision 2

11

•

CoreFIR

: CoreFIR IP is used in the Reloadable Coefficient mode to configure its coefficients on

the fly. CoreFIR IP configuration is as follows:

– Version: 8.5.104

– Filter Type: Single rate fully enumerated

– No of taps: 8

– Coefficients type: Reloadable

– Coefficients bit width: 16 (signed)

– Data bit width: 16 (signed)

– Filter structure: Transposed with no symmetry

TPSRAM IP

TPSRAM IP uses the following configurations:

•

Input signal data buffer

•

Output signal buffer

•

Output signal FFT real data buffer

•

Output signal FFT imaginary data buffer

CoreFFT

CoreFFT IP is used to generate the frequency spectrum of the filtered data. CoreFFT IP configuration is

as follows:

•

Version: 6.3.102

•

FFT Architecture: In place

•

FFT type: Forward

•

FFT Scaling: Conditional

•

FFT Transform Size: 256

•

Width: 16

SYSRESET

SYSRESET IP provides the power-on reset signal.

OSC

OSC IP is configured as an RC oscillator to provide the 50 MHz signal to the CCC (clock conditioning

circuit), narrowband component y(n).

CCC

CCC IP is configured to provide a 100 MHz clock signal

For detailed SmartDesign implementation and resource usage summary, refer to

"Appendix 1:

SmartDesign Implementation" on page 32

.

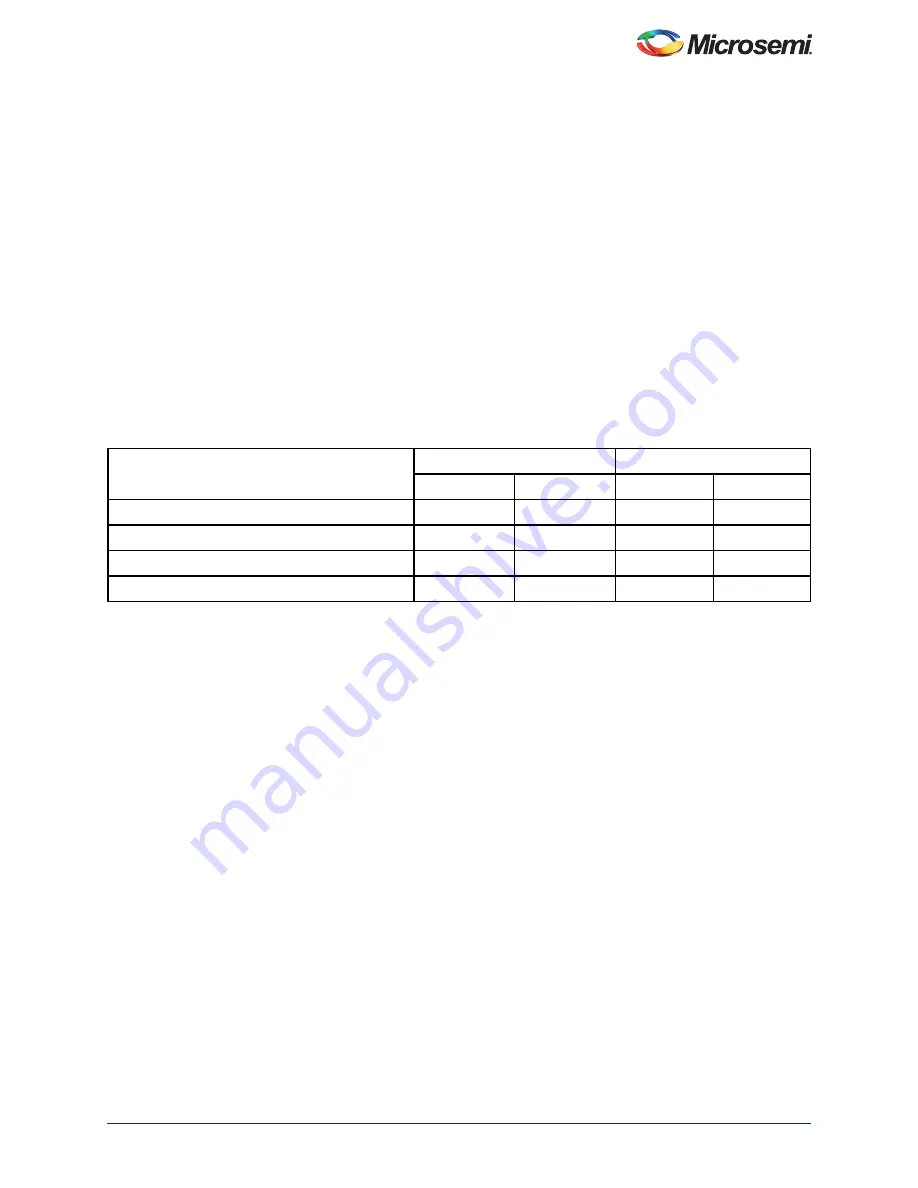

Table 2 •

TPSRAM Configuration for Data Buffers

Buffer

Write Port

Read Port

Depth

Width

Depth

Width

FIR Input Signal

2048

8

1024

16

FIR Output Signal

1024

16

1024

16

FFT Output Real Signal

1024

16

1024

16

FFT Output Imaginary Signal

1024

16

1024

16

Superseded