Nations Technologies Inc.

Tel

:

+86-755-86309900

:

info@nationstech.com

Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North.

Nanshan District, Shenzhen, 518057, P.R.China

597

/

631

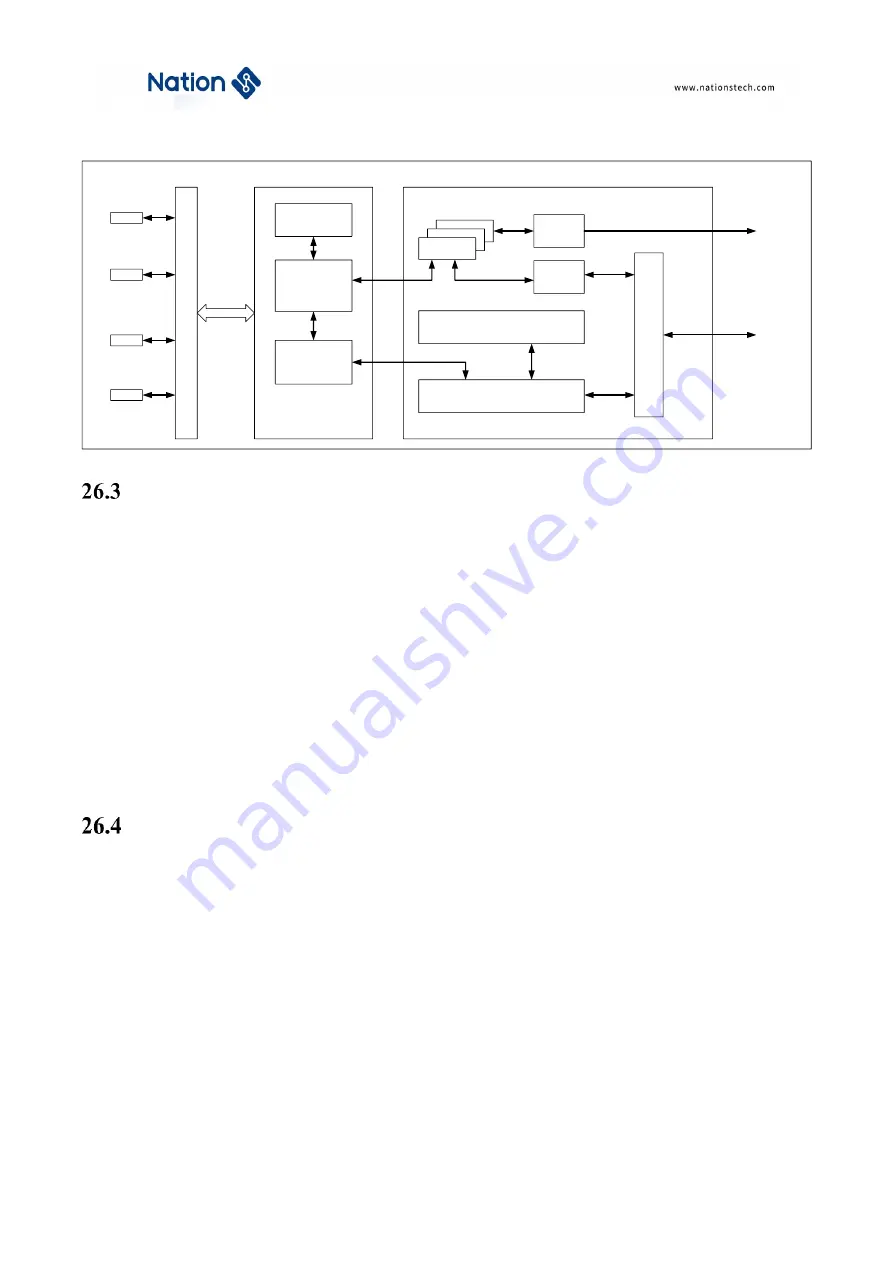

Figure 26-1 USB device block diagram

Clock configuration

The USB 2.0 protocol specification stipulates that the USB full-speed module uses a fixed 48MHz clock. In order to

provide an accurate 48MHz clock to USB_FS_Device, a two-stage clock configuration is required, as follows:

In the first stage, the 48MHz working clock is obtained by accurate frequency division of PLLCLK, so when

using USB_FS_Device, it is necessary to ensure that the PLLCLK clock is 48MHz/72MHz/96MHz, otherwise

USB_FS_Device cannot work normally;

In the second stage, enable the USB peripheral clock mounted on the APB1 bus, that is, the APB1 bus clock. Its

frequency does not have to be equal to 48MHz, but can be greater or less than 48MHz.

Note:

1

、

The frequency of the APB1 bus clock must be greater than 8MHz, otherwise the data buffer may

overflow/underflow.

Functional description

Based on this module, data exchange can be realized between the microcontroller and the PC host through a USB

connection. The data transfer between the microcontroller and the PC host is based on a 512-byte dedicated SRAM,

which is the Packet Buffer Memory in Figure 26-1. USB peripherals can directly access this SRAM. The actual usage

size of this dedicated SRAM is determined by the number of endpoints used and the endpoint packet buffer size of

each endpoint. Each endpoint has a buffer description table entry, which describes the buffer address, size and the

number of bytes that need to be transferred. For details, please refer to 26.4.2 Buffer Description Table. The SRAM

is mapped to the APB1 peripheral memory area, its address is from 0x4000 6000 to 0x4000 63FF, the total capacity

is 1KB, but only 512 bytes are used due to the bus width, and the buffer description table of each endpoint is also

stored in this SRAM, so the maximum endpoint packet buffer that can be used by each endpoint is less than 512

bytes.

Note:

U

S

B

P

H

Y

D+

D-

SIE

Suspend Timer

Packet Buffer

Interface

USB Clock Region

USB_FS_Device

registers

Packet Buffer Memory

Arbiter

A

P

B

1

w

ra

ppe

r

Interrupt

mapper

Register

mapper

APB1 bus

Interrupt request to

NVIC

PCLK1 Clock Region

Gnd

V

bus