R01UH0823EJ0100 Rev.1.00

Page 215 of 1823

Jul 31, 2019

RX23W Group

10. Clock Frequency Accuracy Measurement Circuit (CAC)

10.2.4

CAC Interrupt Request Enable Register (CAICR)

FERRIE Bit (Frequency Error Interrupt Request Enable)

This bit specifies whether the frequency error interrupt request is enabled or disabled.

MENDIE Bit (Measurement End Interrupt Request Enable)

This bit specifies whether the measurement end interrupt request is enabled or disabled.

OVFIE Bit (Overflow Interrupt Request Enable)

This bit specifies whether the overflow interrupt request is enabled or disabled.

Setting this bit to 1 clears the CASTR.FERRF flag.

Setting this bit to 1 clears the CASTR.MENDF flag.

Setting this bit to 1 clears the CASTR.OVFF flag.

Address(es): 0008 B003h

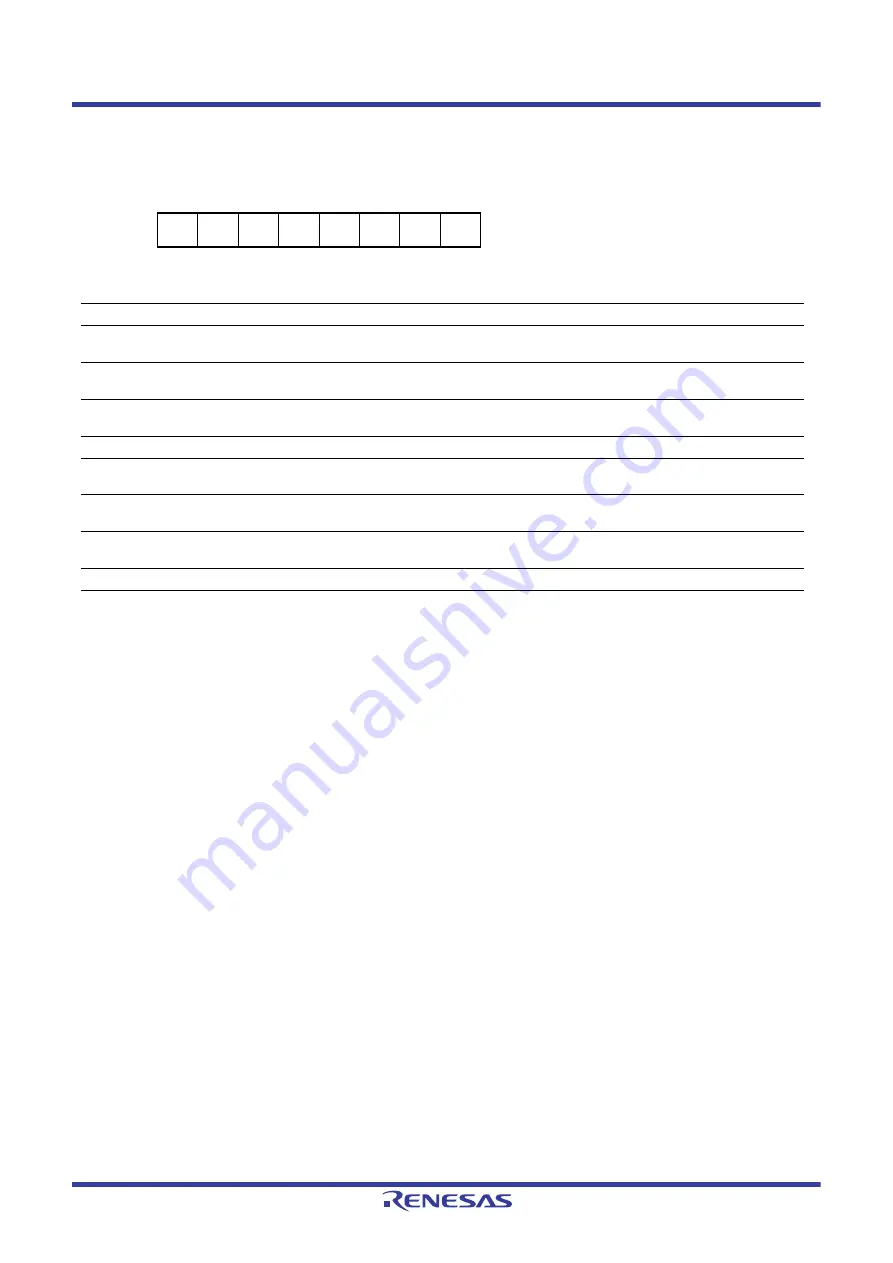

b7

b6

b5

b4

b3

b2

b1

b0

—

OVFFC

L

MENDF

CL

FERRF

CL

—

OVFIE MENDI

E

FERRI

E

Value after reset:

0

0

0

0

0

0

0

0

Bit

Symbol

Bit Name

Description

R/W

b0

Frequency Error Interrupt Request

Enable

0: Frequency error interrupt request is disabled.

1: Frequency error interrupt request is enabled.

R/W

b1

Measurement End Interrupt

Request Enable

0: Measurement end interrupt request is disabled.

1: Measurement end interrupt request is enabled.

R/W

b2

Overflow Interrupt Request Enable 0: Overflow interrupt request is disabled.

1: Overflow interrupt request is enabled.

R/W

b3

—

Reserved

This bit is read as 0. The write value should be 0.

R/W

b4

FERRF Clear

When 1 is written to this bit, the CASTR.FERRF flag is

cleared. This bit is read as 0.

R/W

b5

MENDF Clear

When 1 is written to this bit, the CASTR.MENDF flag is

cleared. This bit is read as 0.

R/W

b6

OVFF Clear

When 1 is written to this bit, the CASTR.OVFF flag is cleared.

This bit is read as 0.

R/W

b7

—

Reserved

This bit is read as 0. The write value should be 0.

R/W