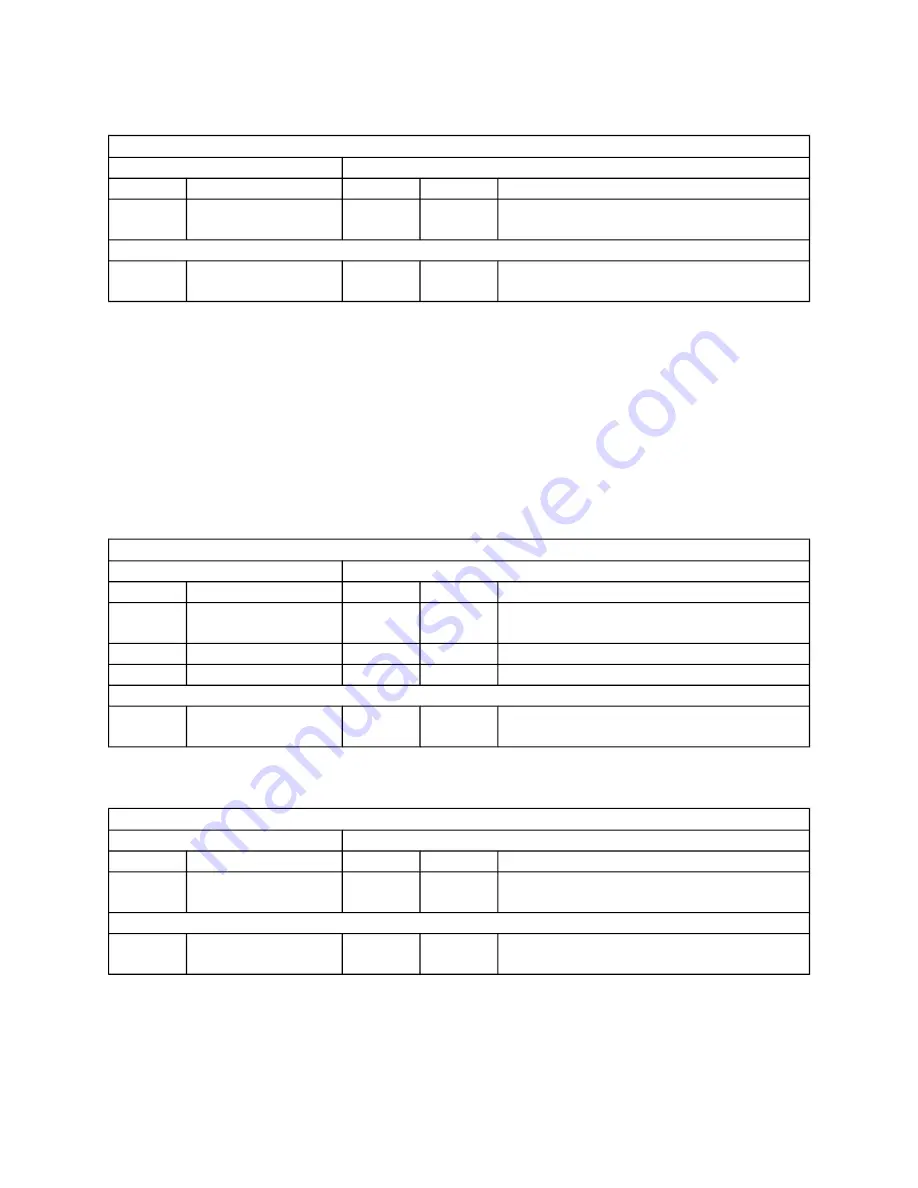

PLIC Interrupt Pending Register 4 (

pending4

)

Base Address

0x0C00_100C

Bits

Field Name

Attr.

Rst.

Description

0

Interrupt 96 Pend-

ing

RO

0

Pending bit for global interrupt 96

…

31

Interrupt 127

Pending

RO

0

Pending bit for global interrupt 127

Table 16:

PLIC Interrupt Pending Register 4

Each global interrupt can be enabled by setting the corresponding bit in the

enables

registers.

The

enables

registers are accessed as a contiguous array of 4 × 32-bit words, packed the

same way as the

pending

bits. Bit 0 of enable word 0 represents the non-existent interrupt ID 0

and is hardwired to 0.

Only 32-bit word accesses are supported by the

enables

array in SiFive RV32 systems.

PLIC Interrupt Enable Register 1 (

enable1

) for Hart 0 M-Mode

Base Address

0x0C00_2000

Bits

Field Name

Attr.

Rst.

Description

0

Interrupt 0 Enable

RO

0

Non-existent global interrupt 0 is hard-

wired to zero

1

Interrupt 1 Enable

RW

X

Enable bit for global interrupt 1

2

Interrupt 2 Enable

RW

X

Enable bit for global interrupt 2

…

31

Interrupt 31

Enable

RW

X

Enable bit for global interrupt 31

Table 17:

PLIC Interrupt Enable Register 1 for Hart 0 M-Mode

PLIC Interrupt Enable Register 4 (

enable4

) for Hart 0 M-Mode

Base Address

0x0C00_200C

Bits

Field Name

Attr.

Rst.

Description

0

Interrupt 96

Enable

RW

X

Enable bit for global interrupt 96

…

31

Interrupt 127

Enable

RW

X

Enable bit for global interrupt 127

Table 18:

PLIC Interrupt Enable Register 4 for Hart 0 M-Mode

Copyright © 2017–2018, SiFive Inc. All rights reserved.

27