DNx-SL-514 Synchronous Serial Interface Board

Chapter 3

26

Programming with the Low-Level API

May 2018

www.ueidaq.com

508.921.4600

© Copyright 2018

United Electronic Industries, Inc.

typedef struct {

uint32 ch_status; // channel status

uint32 flags; // <Reserved>

} L514_STATUS, *pL514_STATUS;

The

ch_status

element is encoded with status flags described in

.

NOTE:

Note that some bits are sticky and are cleared after the status is read,

and some are static and return the current status value. Sticky bits are

indicated in the bit descriptions.

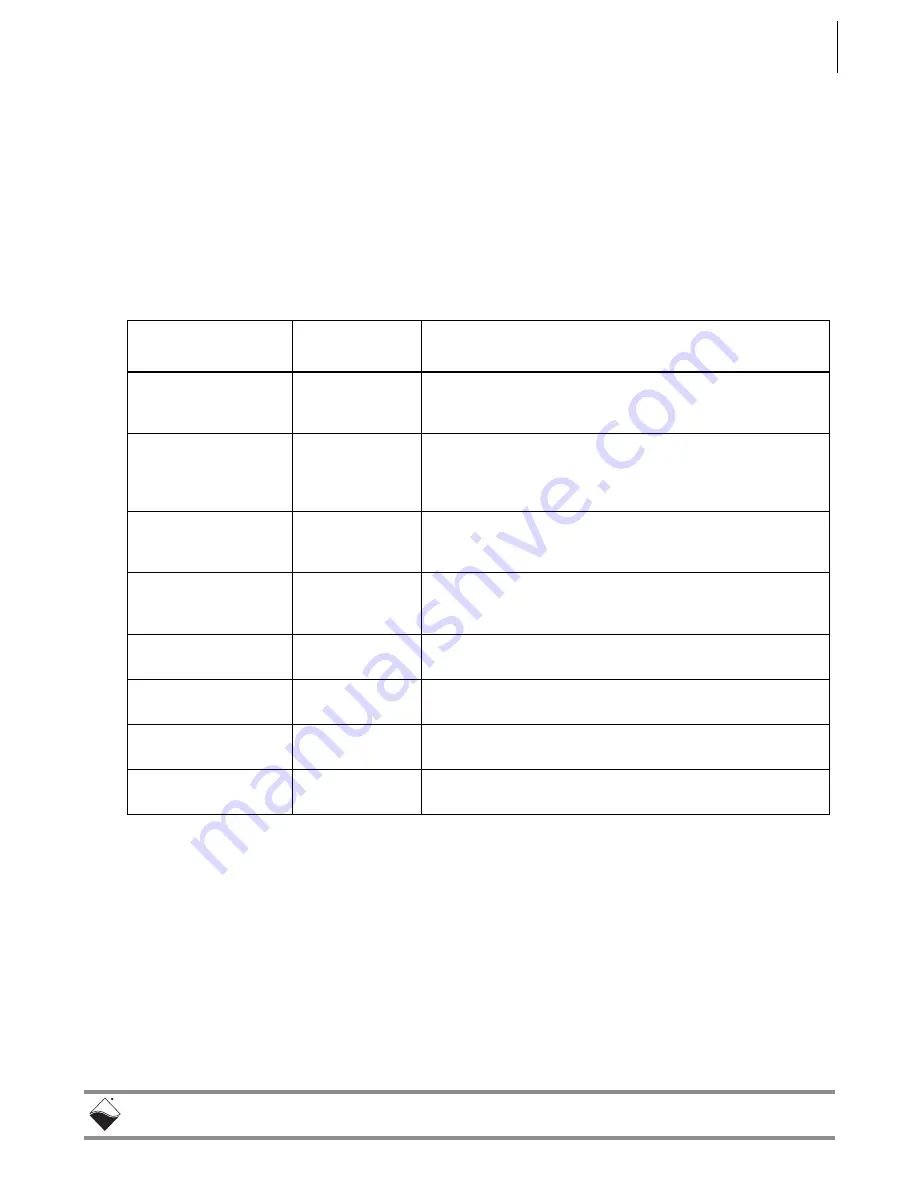

#defined

Value

Bit

Representation

Description

SL514_CSTS_TXERR

(1L<<19)

Slave TX Timing Error:

• 1= error detected, master clock arrived too early

(sticky bit, cleared after read)

SL514_CSTS_RXERR

(1L<<18)

Master RX Timing Error:

• 1= error detected, slave drove RX data high during mono-

flop time

(sticky bit, cleared after read)

SL514_CSTS_TXFE

(1L<<17)

Slave TX FIFO is empty:

• 1= FIFO empty

(sticky bit, cleared after read)

SL514_CSTS_RXFF

(1L<<16)

Master RX FIFO is full:

• 1= FIFO full

(sticky bit, cleared after read)

SL514_CSTS_TXBSY

(1L<<3)

Slave TX is transmitting data:

• 1= sending data

SL514_CSTS_RXBSY

(1L<<2)

Master RX is receiving data:

• 1= receiving data

SL514_CSTS_TXFHF

(1L<<1)

Slave TX is below watermark:

• 1= below watermark

SL514_CSTS_RXFHF

(1L<<0)

Master RX is above watermark:

• 1= above watermark

Table 3-3 SL-514

Status Bit Meanings