50

Virtex-6 FPGA System Monitor

UG370 (v1.1) June 14, 2010

Application Guidelines

SYSMON I/O

For this design the SYSMON I/Os listed in

are used.

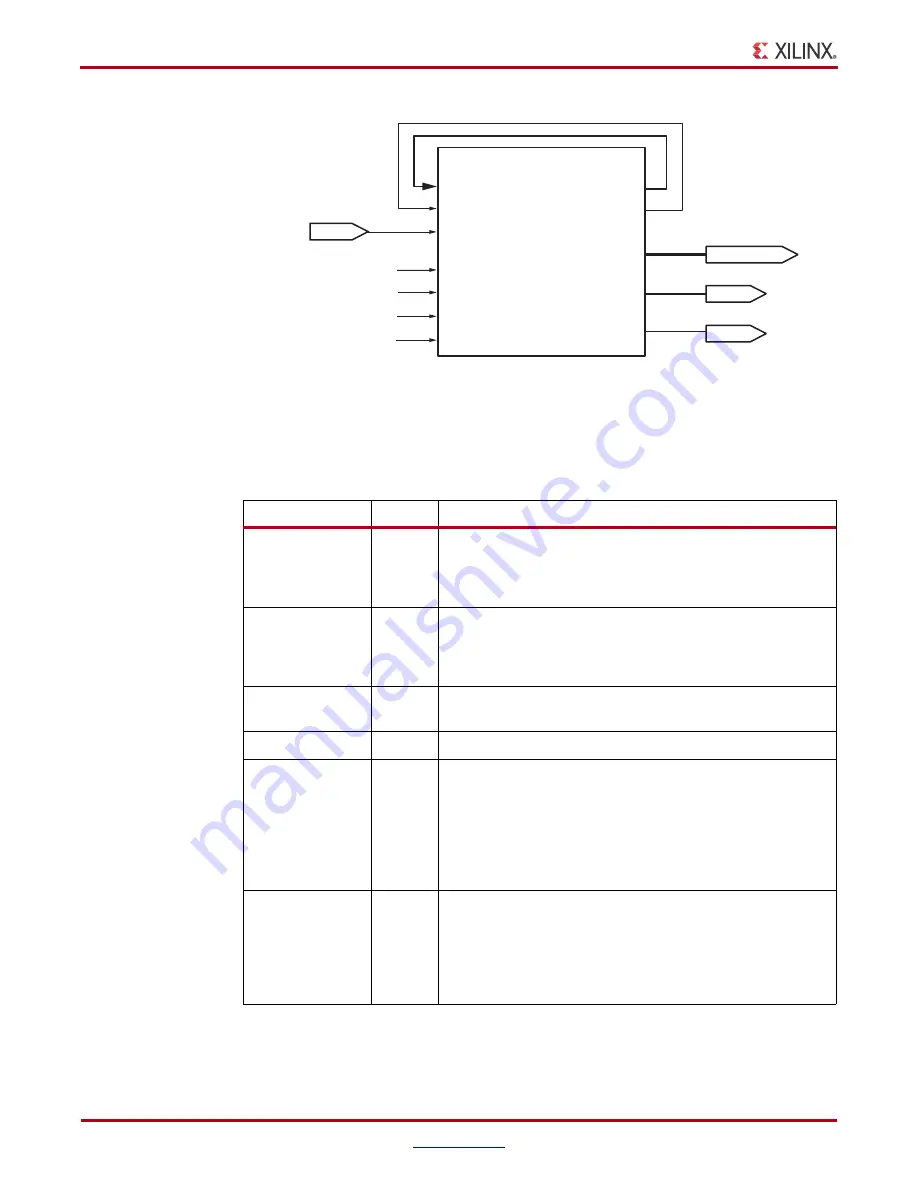

X-Ref Target - Figure 29

Figure 29:

System Monitor Sample Design

DO[15:6]

DADDR[4:0]

DWE

RESET

DEN

CHANNEL[4:0]

DCLK

50 MHz

External Clock

ALM[2]

EOS

BUSY

SYSMON

DADDR[5]

DADDR[6]

0

0

0

0

clk

busy

alarm

V

CCAUX

[9:0]

10-Bit V

CCAUX

Measurement

(3 mV / LSB)

UG370_29_060809

Table 20:

SYSMON I/Os

Name

I/O

Description

DADDR[6:0]

Inputs

DRP address bus. The status registers (for example,

measurement results) are accessed via the DRP. In this sample

design, the CHANNEL[4:0] bus is connected to DADDR[4:0]

and DADDR[6:5] are connected to logic 0.

DEN

Input

DRP enable signal. When High, the address on DADDR[6:0]

is latched, and the contents of the corresponding register is

placed on the DO[15:0] bus. In this example, DEN is connect

to EOS.

DWE

Input

DRP write enable. Since no writes take place to the DRP, this

input is held at logic 0.

RESET

Input

SYSMON reset signal. It is tied to logic 0 in this example.

CHANNEL[4:0]

Output

ADC input multiplexer address. The ADC input multiplexer

address is placed on this bus at the end of the conversion

when BUSY transitions Low (refer to

). Because the results of input MUX address

02h

(V

CCAUX

) are placed in the status register at DRP address

02h

, these outputs can be used to drive the DADDR[6:0]

inputs to access the V

CCAUX

result.

EOS

Output

End-of-Sequence output. EOS pulses High for one DCLK

cycle at the end of a full channel sequence. In this example,

VCCAUX is the last channel in the sequence, allowing EOS to

be used as an input to DEN to latch the address on

DADDR[6:0] and enable the contents of Status register

02h

onto the DO bus for reading.

www.BDTIC.com/XILINX