XRM(2)-DAC-D4/1G User Guide

V2.2 - Mar 8, 2018

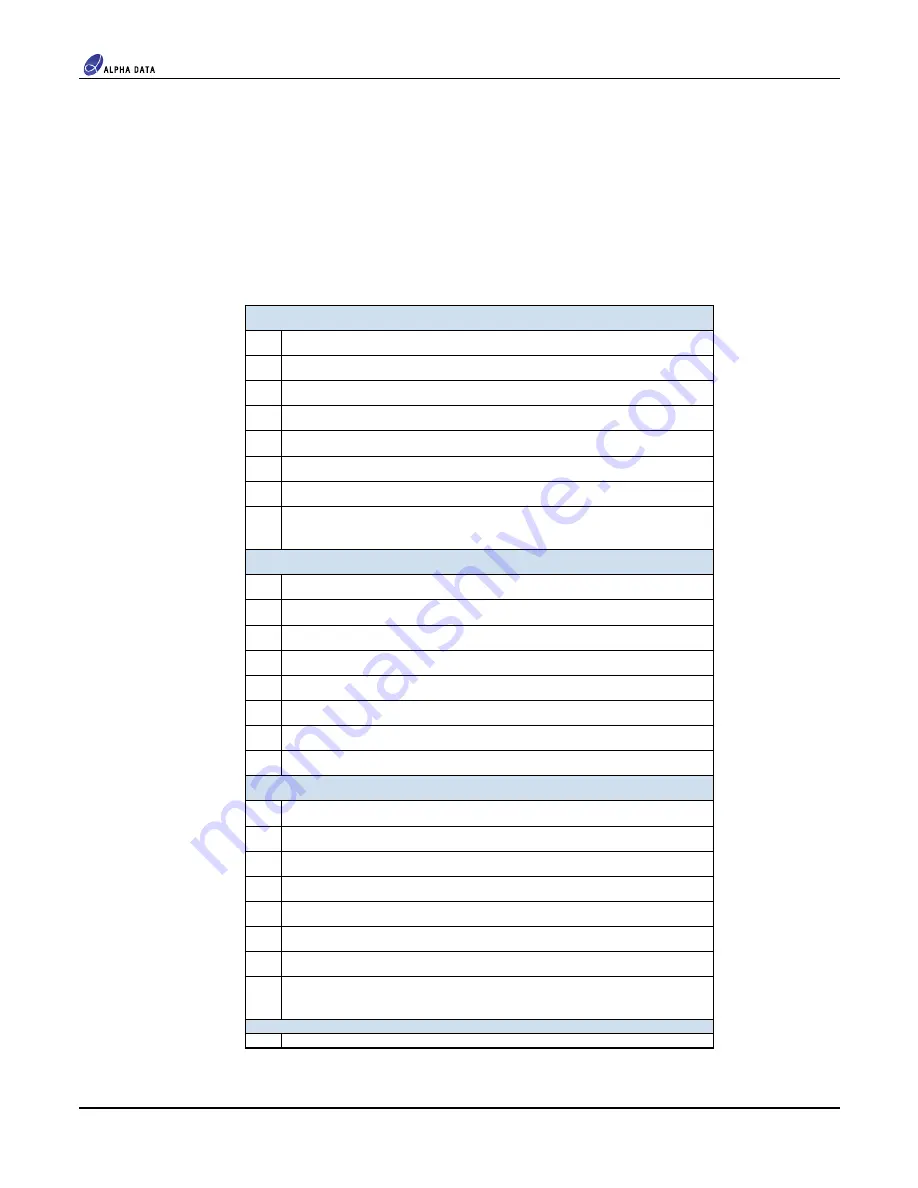

4.30 PHASE_VALUE_REG (0x1F)

This register provides two 16 bit values which are sign-extended versions of the 9 bit phase alignment settings.

By default. the values returned are the mid-point of the phase window ( lower 16 bits) and the width of the

window (upper 16 bits), which is centred on the mid-point value. Setting bit 0 of the AUXCNTRL_REG above

switches this to provide the start point of the valid phase window ( lower 16 bits) and the end point of the valid

phase window ( upper 16 bits).

This value is valid only for Virtex4 and Virtex5 designs. For Virtex6 and later, this register always returns a fixed

value as no phase alignment is required

D31 to D24:

D31 sign bit copy

D30 sign bit copy

D29 sign bit copy

D28 sign bit copy

D27 sign bit copy

D26 sign bit copy

D25 sign bit copy

D24

D8 (sign and magnitude) of width (end point) of valid DCM phase

window

D23 to D16:

D23 D7 of width (end point) of valid DCM phase window

D22 D6 of width (end point) of valid DCM phase window

D21 D5 of width (end point) of valid DCM phase window

D20 D4 of width (end point) of valid DCM phase window

D19 D3 of width (end point) of valid DCM phase window

D18 D2 of width (end point) of valid DCM phase window

D17 D1 of width (end point) of valid DCM phase window

D16 D0 of width (end hoint) of valid DCM phase window

D15 to D8:

D15 sign bit copy

D14 sign bit copy

D13 sign bit copy

D12 sign bit copy

D11 sign bit copy

D10 sign bit copy

D9

sign bit copy

D8

D8 (sign and magnitude) of mid-point (start point) of valid DCM

phase window

D7 to D0:

D7

D7 mid point (start point) of valid DCM phase window

Page 86

Register Description

xrm-dac-d4-1g-manual_v2_2.pdf