UG-1262

Rev. B | Page 172 of 312

Table 195. CHNL_CFG for Primary Data Structure in Peripheral Scatter Gather Mode, CHNL_CFG, Bits[2:0] = 110

Bit(s) Name

Description

[31:30]

DST_INC

Set to 10, configures the controller to use word increments for the address.

[29:28]

Reserved

Undefined. Write as 0.

[27:26]

SRC_INC

Set to 10, configures the controller to use word increments for the address.

[25:24]

SRC_SIZE

Set to 10, configures the controller to use word transfers.

[23:18]

Reserved

Undefined. Write as 0.

[17:14]

R_POWER

Set to 0010, indicates that the DMA controller performed four transfers without rearbitration.

[13:4]

N_MINUS_1

Configures the controller to perform N DMA transfers, where N is a multiple of four.

3

Reserved

Undefined. Write as 0.

[2:0]

CYCLE_CTRL

Set to 110, configures the controller to perform a peripheral scatter gather DMA cycle.

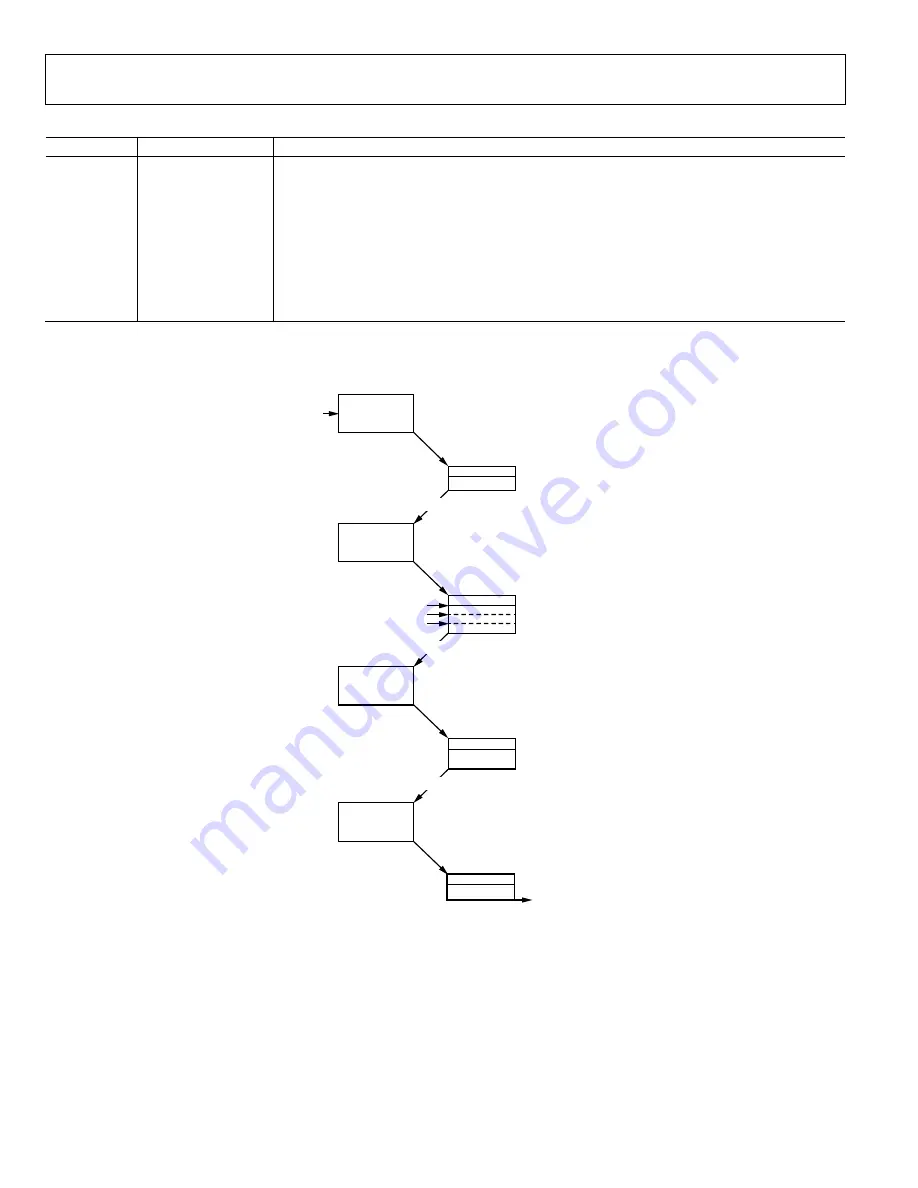

PRIMARY

ALTERNATE

NOTES

1. FOR ALL PRIMARY TO ALTERNATE TRANSITIONS, THE CONTROLLER

DOES NOT ENTER THE ARBITRATION PROCESS AND IMMEDIATELY

PERFORMS THE DMA TRANSFER THAT THE ALTERNATE CHANNEL

CONTROL DATA STRUCTURE SPECIFIES.

REQUEST

TASK A

REQUESTS

TASK B

TASK C

TASK D

REQUESTS

REQUESTS

N = 4, 2

R

= 4

DMA_DONE[C]

N = 5, 2

R

= 8

N = 8, 2

R

= 2

N = 3, 2

R

= 4

REQUESTS

COPY FROM A

IN MEMORY TO

ALTERNATE

COPY FROM B

IN MEMORY TO

ALTERNATE

COPY FROM C

IN MEMORY TO

ALTERNATE

COPY FROM D

IN MEMORY TO

ALTERNATE

1667

5-

241

Figure 47. Peripheral Scatter Gather DMA Transfer