Programmers Model

ARM DDI 0432C

Copyright © 2009 ARM Limited. All rights reserved.

3-7

ID112415

Non-Confidential

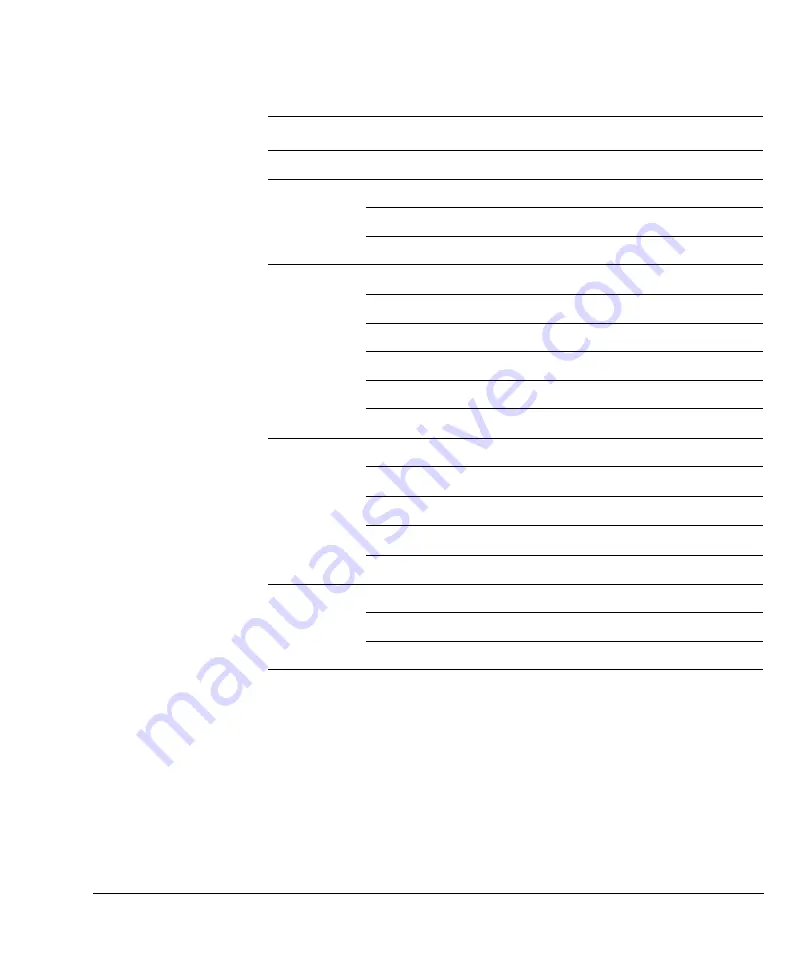

See the

ARMv6-M ARM

for more information about the ARMv6-M Thumb instructions

Extend

Unsigned byte

UXTB

Rd

,

Rm

1

Reverse

Bytes in word

REV

Rd

,

Rm

1

Bytes in both halfwords

REV16

Rd

,

Rm

1

Signed bottom half word

REVSH

Rd

,

Rm

1

State change

Supervisor Call

SVC #<imm>

-

e

Disable interrupts

CPSID i

1

Enable interrupts

CPSIE i

1

Read special register

MRS Rd, <specreg>

4

Write special register

MSR <specreg>, Rn

4

Breakpoint

BKPT #<imm>

-

Hint

Send event

SEV

1

Wait for event

WFE

2

f

Wait for interrupt

WFI

Yield

YIELD

g

1

No operation

NOP

1

Barriers

Instruction synchronization

ISB

4

Data memory

DMB

4

Data synchronization

DSB

4

a. Depends on multiplier implementation.

b. N is the number of elements.

c. N is the number of elements in the stack-pop list including PC and assumes load or store

does not generate a HardFault exception.

d. 3 if taken, 1 if not-taken.

e. Cycle count depends on core and debug configuration.

f. Excludes time spent waiting for an interrupt or event.

g. Executes as NOP.

Table 3-1 Cortex-M0 instruction summary (continued)

Operation Description

Assembler

Cycles