Programming Manual

A-1

The CW-P Series supports the IEEE 488.2 and SCPI 1993.0 status reporting data

structures. These structures are comprised of status registers and status register

enable mask pairs. These pairs are described below:

The Status Byte status register can be read by the *STB? command or by issuing a

GPIB serial poll. Either operation clears the contents of the Status Byte. The *CLS

command clears the Status Byte.

The CW-P Series unit can be configured to request service from the GPIB controller by

setting the appropriate bits in the Service Request Enable register. The SRE register

has the same bit pattern as the Status Byte. The SRE register is modified using the

*SRE command, and can be read with the *SRE? command. For example, if the SRE

register is set to 0x10 (MAV), when the CW-P unit has a message available, the Status

Byte register will contain 0x50 (RQS and MAV) and the SRQ line of the GPIB bus will

be pulled low indicating a request for service.

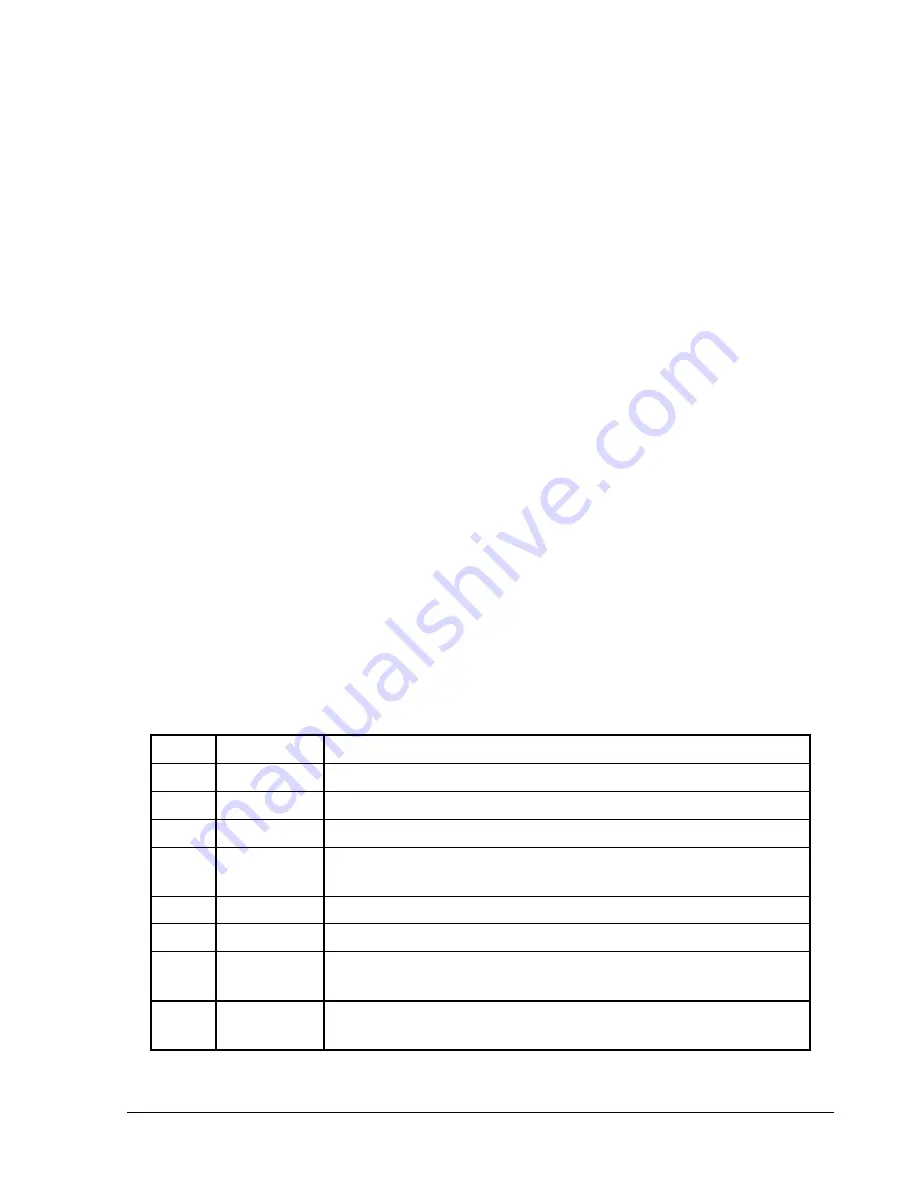

Bit

Hex Value Description

0

01

Not used.

1

02

Not used.

2

04

Error/event queue message available.

3

08

Questionable Status flag. Indicates quality of current data

being acquired. This bit is not used.

4

10

Message available (MAV).

5

20

Standard Event Status Register (ESR).

6

40

Request Service flag (RQS) for serial polling, or Master

Summary Status (MSS) in response to

*STB?

7

80

Operation Status flag. Indicates the current operational

state of the unit. This bit is not used.

Summary of Contents for CW 1251P

Page 2: ......