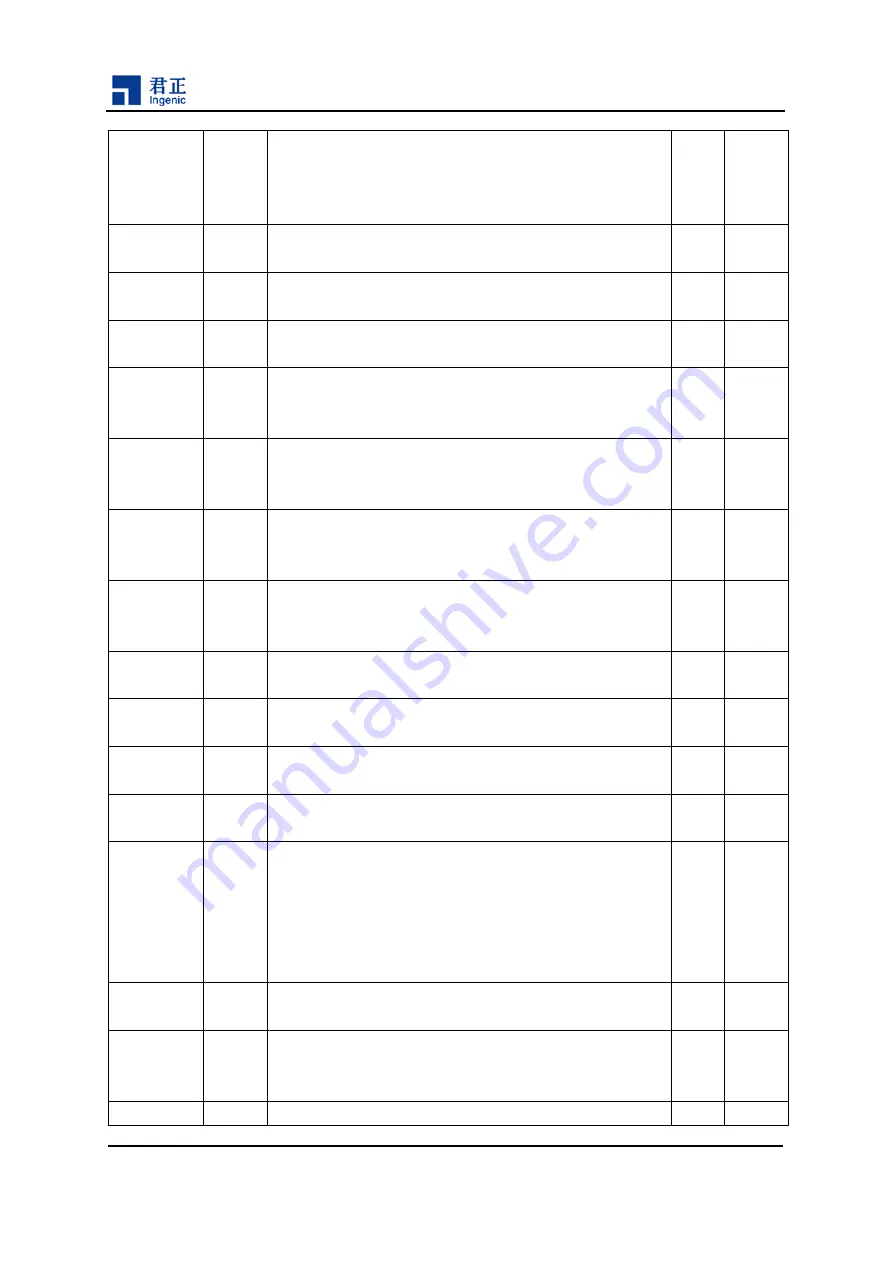

CP0

LSNM

28

Controls access of load/store between dseg and remaining

memory when the dseg segment is present:

0: Load/store in dseg range goes to dseg.

1: Load/store in dseg range goes to main memory.

R/W

0

Doze

27

Read as zero, indicating that the feature is not

implemented.

R

0

Halt

26

Read as zero, indicating that the feature is not

implemented.

R

0

CountDM

25

The

Count

register behavior in Debug Mode.

1: Count register is normally running in Debug Mode.

R

1

IBusEP

24

In Debug Mode, Bus error exception not applies to a

Debug Mode Bus Error exception, this bit is read-only(R)

and read as zero.

R

0

MCheckP

23

In Debug Mode, a Machine Check exception not applies to

a Debug Mode Machine Check exception, and this bit is

read-only(R) and reads as zero.

R

0

CacheEP

22

In Debug Mode, a Cache Error exception not applies to a

Debug Mode Cache Error exception.

This bit is read-only(R) and read as zero.

R

0

DBusEP

21

In Debug Mode, a Bus Error exception not applies to a

Debug Mode Cache Error exception.

This bit is read-only(R) and read as zero.

R

0

IEXI

20

An imprecise Error Exception Inhibit (IEXI) is not

implemented. This bit is read-only(R) and reads as zero.

R

0

DDBSImpr

19

A Debug Data Break Store Imprecise exception is not

implemented, this bit read as zero.

R

0

DDBLImpr

18

A Debug Data Break Load Imprecise exception is not

implemented, this bit read as zero.

R

0

EJTAGVer

17:15

JTAG version.

0: Version 2.0

R

0

DExcCode

14:10

Indicates the cause of the latest exception in debug mode.

The field is encoded as the ExcCode field in the Cause

register for those exceptions that can occur in Debug

Mode, with addition of code 30 with the mnemonic

CacheErr for cache errors and the use of code 9 with

mnemonic Bp for the SDBBP instruction.

R

0

NoSSt

9

Read always as zero, indicating that Single step feature is

available.

R

0

SSt

8

Controls whether single-step feature is enabled:

0: No debug single-step exception enabled.

1: Debug single step exception enabled.

R/W

0

OffLine

7

MIPS MT processors is not implemented, this bit is

R

0

XBurst®2

CPU Core Programming Manual

Copyright © 2005-2020 Ingenic Semiconductor Co., Ltd. All rights reserved.

49