Service Information

5-10

ID data circuits

Upon power-up, card identif cation information from each

card is read by the mainframe. This ID data includes such

information as card ID, hardware settling time, and relay

conf guration information.

ID data is contained within an on-card EEPROM (U107). In

order to read this information, the sequence described below

is performed on power-up.

1. The IDDATA line (pin 5 of U107) is set from high to low

while the IDCLK line (pin 6 of U107) is held high. This

action initiates a start command to the ROM to transmit

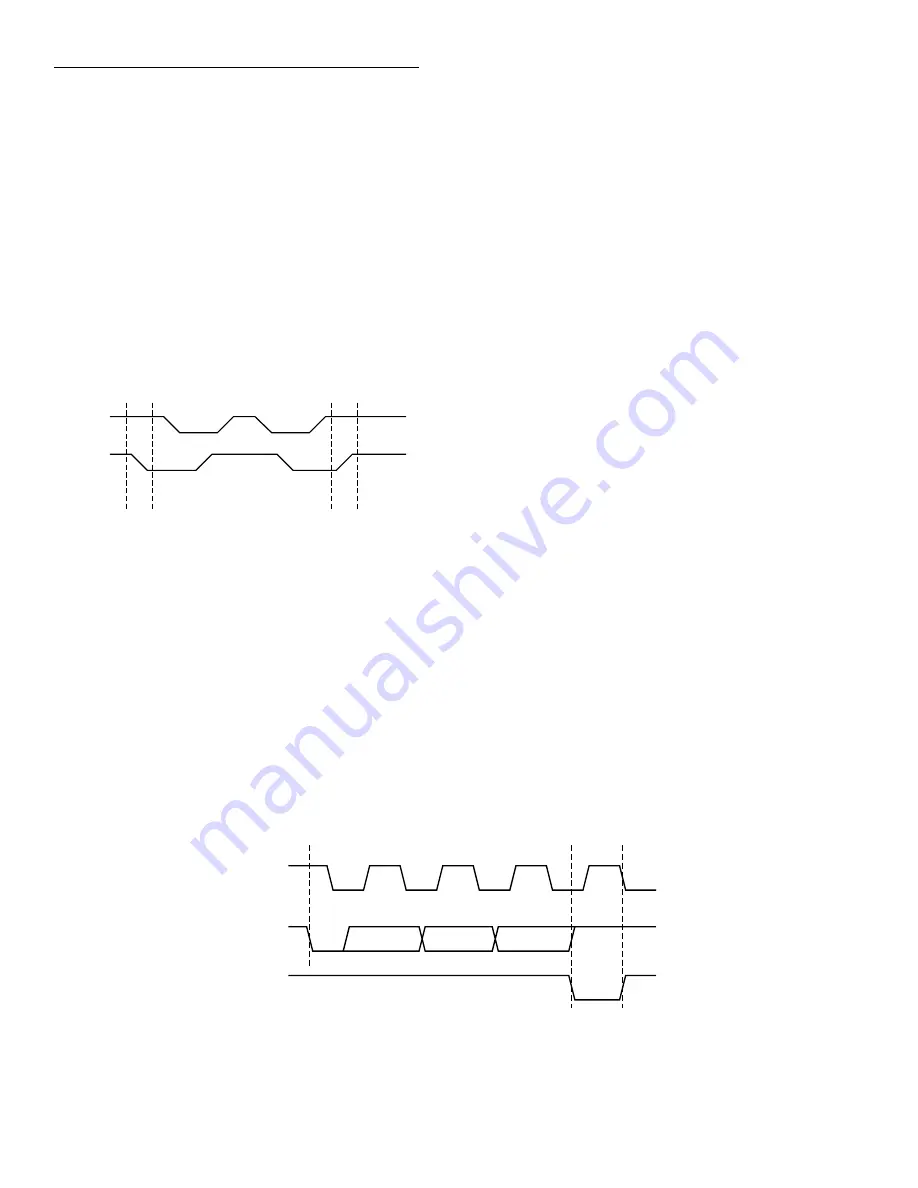

data serially to the mainframe (Figure 5-7).

Figure 5-7

Start and stop sequences

2. The mainframe sends the ROM address location to be

read over the IDDATA line. The ROM then transmits an

acknowledge signal back to the mainframe, and it then

transmits data at that location back to the mainframe

(Figure 5-8).

3. The mainframe then transmits an acknowledge signal,

indicating that it requires more data. The ROM will then

sequentially transmit data after each acknowledge sig-

nal it receives.

4. Once all data is received, the mainframe sends a stop

command, which is a low-to-high transition of the

IDDATA line with the IDCLK line held high

(Figure 5-7).

Relay control

Card relays are controlled by serial data transmitted via the

relay DATA line. A total of f ve bytes for each card are

shifted in serial fashion into latches located in the card relay

driver ICs. The serial data is clocked in by the CLK line. As

data overf ows one register, it is fed out the Q’s line of the

register down the chain.

Once all f ve bytes have shifted into the card, the STROBE

line is set high to latch the relay information into the Q out-

puts of the relay drivers, and the appropriate relays are ener-

gized (assuming the driver outputs are enabled, as discussed

below). Note that a relay driver output goes low to energize

the corresponding relay.

Relay power control

A relay power control circuit, made up of Q101, Q102,

U106, U108, and associated components, keeps power dissi-

pated in relay coils at a minimum, thus reducing possible

problems caused by thermal EMFs.

During steady-state operation, the relay supply voltage, +V,

is regulated to +3.5V to minimize coil power dissipation.

When a relay is f rst closed, the STROBE pulse applied to

U106 changes the parameters of the relay supply voltage reg-

ulator, Q101, allowing the relay supply voltage, +V, to rise to

+5.7V for about 100msec. This brief voltage rise ensures that

relays close as quickly as possible. After the 100msec period

has elapsed, the relay supply voltage (+V) drops back down

to its nominal steady-state value of +3.5V.

Figure 5-8

Transmit and acknowledge sequence

ID CLK

ID DATA

Start Bit

Stop Bit

ID CLK

Acknowledge

Start

1

8

9

(Data output

from mainframe

or ROM)

IDDATA

(Data output

from mainframe

or ROM)

IDDATA