56

The 68000's Instruction Set

high-order bit of the operand (i.e., bit 7) is set. This operation is

indivisible

and uses a read-modify-write cycle. Its principal

application is in multiprocessor systems.

Application:

The

TAS

instruction permits one processor in a multiprocessor

system to test a resource (e.g., shared memory) and claim the

resource if it is free. The most-significant bit of the byte at the

effective address is used as a semaphore to indicate whether the

shared resource is free. The

TAS

instruction reads the semaphore

bit to find the state of the resource, and then sets the semaphore

to claim the resource (if it was free). Because the operation is

indivisible, no other processor can access the memory between

the testing of the bit and its subsequent setting.

Condition codes:

X N Z V C

- * * 0 0

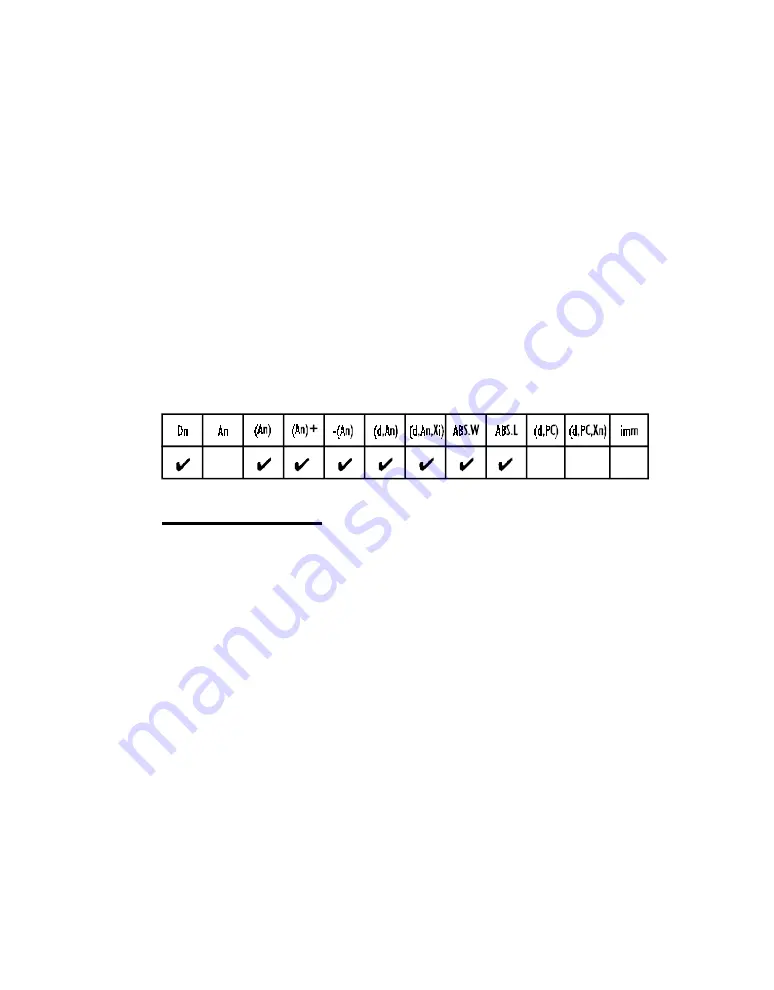

Source operand addressing modes

TRAP

Trap

Operation:

S

←

1;

[SSP]

←

[SSP] - 4; [M([SSP])]

←

[PC];

[SSP]

←

[SSP] - 2; [M([SSP])]

←

[SR];

[PC]

←

vector

Syntax:

TRAP #<vector>

Attributes:

Unsized

Description:

This instruction forces the processor to initiate exception

processing. The vector number used by the

TRAP

instruction is in

the range 0 to 15 and, therefore, supports 16 traps (i.e.,

TRAP

#0

to

TRAP

#15

).

Application:

The

TRAP

instruction is used to perform operating system calls

and is system independent. That is, the effect of the call depends

on the particular operating environment. For example, the

University of Teesside 68000 simulator uses

TRAP

#15

to perform

Summary of Contents for 68000

Page 1: ...Motorola 68000 s Instruction Set ...

Page 2: ......