NXP Semiconductors

UM11637

FRDMGD3160DCMHB evaluation board

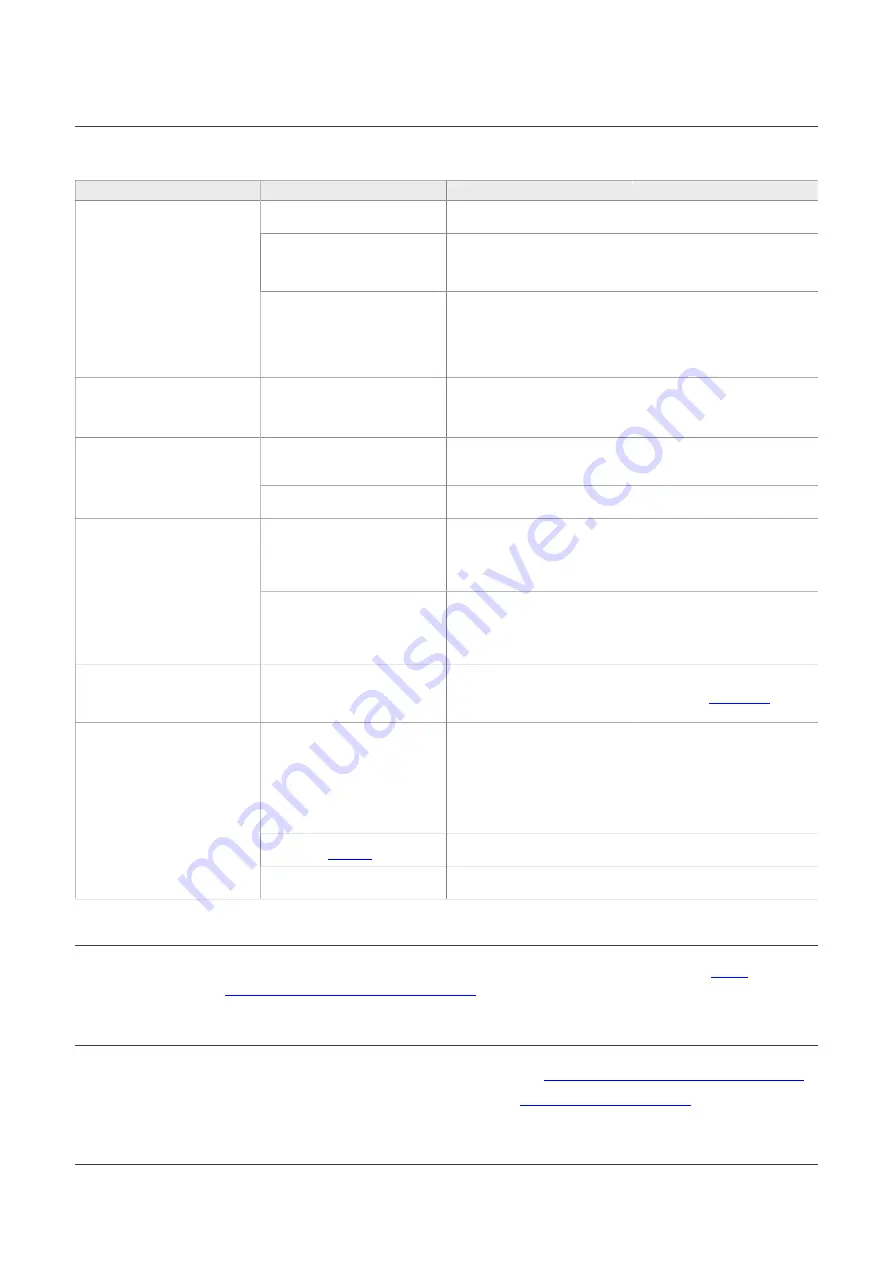

Problem

Evaluation

Explanation

Corrective action(s)

Check bit length of message sent

There is SPIERR if SCLK does not

see a n*24 multiple of cycles

Use 24-bit message length for SPI

messages

Check CRC

SPIERR faults if CRC provided in

sent message is not good

Use FlexGUI to generate commands

with valid CRC. The command can be

copied in binary or hexadecimal and

sent from another program.

SPIERR reported after SPI message

Check for sufficient dead time

between SPI messages

SPIERR fault bit is set when the time

between SPI messages (txfer_delay)

received is too short. Minimum

required delay time is 19 µs.

Check time between CSB rising edge

(old message end) and CSB falling

edge (new message start) during

normal SPI read, and ensure transfer

delay dead time check.

SPIERR can also be cleared in BIST.

VCCREGUV reported on startup

Check VCCREG potential

Caused by low VCC

Clear VCCREGUV fault bit

(STATUS1).

Tune VCC-GNDISO potential with

power supply potentiometer (R65).

Check HV domain is powered

correctly

Related to slow rise time of VCC

supply on HV domain, or failed VREF

regulator

Clear VREFUV bit (STATUS2).

Reset HV domain supply if fault bit

does not clear.

VREFUV reported on startup

Check VCC for undervoltage

condition

Low VCC is visible indirectly through

other HV domain faults

Tune VCC-GNDISO using R65

potentiometer.

Check VEE level on suspect domain. If VEE level is not at desired negative

voltage it could cause excessive VCC

level.

Check Zener diode in power supply

circuit for proper value in setting VEE

level.

Clear VCCOV bit (STATUS1) to

continue.

VCCOV fault reported on startup

Check VCC-GNDISO potential

PWM is disabled during a VCC

overvoltage (20 V nom.)

Tune VCC-GNDISO potential to

suitable level with power supply set

potentiometer (R65).

Clear VCCOV bit (STATUS1) to

continue.

No PWM during short circuit test

Check PWMxSEL jumpers

Incorrect configuration of PWMALT

pins prevent short-circuit test by

enforcing dead time

For short-circuit test, set PWMLSEL

(J10) and PWMHSEL (J11) to bypass

dead time. See

for

details.

Check VSUP/VDD for undervoltage

condition

VDD_UV latches SPI buffer contents,

preventing updated fault reporting.

Check voltage provided at VDD pin

(pin 3).

On each read, compare the address

from the sent command and response

(a difference indicates that the SPI

response is latched due to inactive).

Read multiple addresses to ensure a

good comparison.

Check PS_EN is set to HIGH in

VCC/VEE can be enabled/disabled in

software.

Enable VCC/VEE from FlexGUI

Bad SPI data, appears to repeat

previous response

Check VCC for undervoltage

Unpowered VCC prevents HV domain

from updating data

Tune VCC-GNDISO using R65

potentiometer

7 Schematics, board layout, and bill of materials

The board schematics, board layout, and bill of materials are available at

on the Overview tab under Get Started.

8 References

[1] Tool summary page for FRDMGD3160DCMHB

http://www.nxp.com/FRDMGD3160DCMHB

[2] Product summary page for GD3160 device

UM11637

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2022. All rights reserved.

User guide

Rev. 2 — 3 February 2022

39 / 42