34

www.xilinx.com

Ethernet 1000BASE-X PCS/PMA or SGMII v7.0

UG145 January 18, 2006

Chapter 4:

Detailed Example Design

R

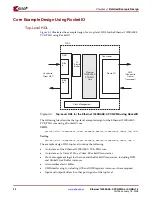

Demonstration Test Bench

Figure 4-4

illustrates the demonstration test bench for the Ethernet 1000BASE-X PCS/PMA

using RocketIO.

The following files describe the demonstration test bench.

VHDL

project_dir>

/

<component_name>

/simulation/

demo_tb.vhd

Verilog

project_dir>

/

<component_name>

/simulation/

demo_tb.v

The demonstration test bench is a simple VHDL or Verilog program to exercise the

example design and the core itself.

Core with MDIO Interface

The demonstration test bench performs the following tasks:

•

Input clock signals are generated.

•

A reset is applied to the example design.

Figure 4-4:

Demonstration Test Bench Using RocketIO

PMA

Monitor

(serial to parallel

conversion and

8B10B

decoding)

PMA

Stimulus

(8B10B encoding

and parallel to

serial

conversion)

GMII

Stimulus

GMII

Monitor

GMII

RocketIO

DUT

Demonstration Test Bench

Control and Data Structures

Configuration

Stimulus