38

www.xilinx.com

Ethernet 1000BASE-X PCS/PMA or SGMII v7.0

UG145 January 18, 2006

Chapter 4:

Detailed Example Design

R

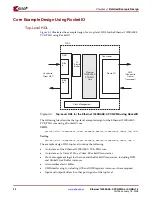

Demonstration Test Bench

Figure 4-6

illustrates the demonstration test bench for the Ethernet 1000BASE-X PCS with

TBI.

The demonstration test bench is described in the following files:

VHDL

project_dir>

/

<component_name>

/simulation/

demo_tb.vhd

Verilog

project_dir>

/

<component_name>

/simulation/

demo_tb.v

The demonstration test bench is a simple VHDL or Verilog program to exercise the

example design and the core itself.

Core with MDIO Interface

The demonstration test bench performs the following tasks.

•

Input clock signals are generated.

•

A reset is applied to the example design.

•

The Ethernet 1000BASE-X PCS/PMA core is configured through the MDIO interface

by injecting an MDIO frame into the example design. This disables Auto-Negotiation

(if present) and takes the core out of the Isolate state.

Figure 4-6:

Demonstration Test Bench for the Ethernet 1000BASE-X PCS with TBI

TBI

Monitor

(8B10B

decoding)

TBI

Stimulus

(8B10B

encoding)

GMII

Stimulus

GMII

Monitor

GMII

TBI

DUT

Demonstration Testbench

Control and Data Structures

Configuration

Stimulus