IOS-EP2 I/O SERVER MODULE Cyclone II Based FPGA Module

___________________________________________________________________

__________________________________________________________________________

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com http://www.acromag.com

15

Control Register (Read/Write) - (Base Addr + 00H)

This read/write register is used to transfer control back to configuration

mode when in user mode, set your specific model of the IOS-EP2, and issue

a software reset.

Bit-0 controls operation of the IOS-EP2 module in user mode and

configuration mode via control of pin F3 of the Altera FPGA. When bit-0 is

set to logic low the IOS-EP2 module will be in user mode. Setting bit-0 to a

logic high places the IOS-EP2 Series in configuration mode. Upon issue of

an IOS bus reset, this register bit will be clear placing the IOS-EP2 in user

mode. Also, initial configuration of the Altera FPGA sets bit-0 to a logic low

holding the FPGA in user mode.

Bits 10 to 8 are used to set the IOS-EP2 model corresponding to your I/O

mix. This will allow the Altera FPGA to properly map Input/Output registers

to the I/O transceivers present on your module. Bits 10 to 8 should be set

as identified in the following table to identify the model corresponding to

your IOS-EP2.

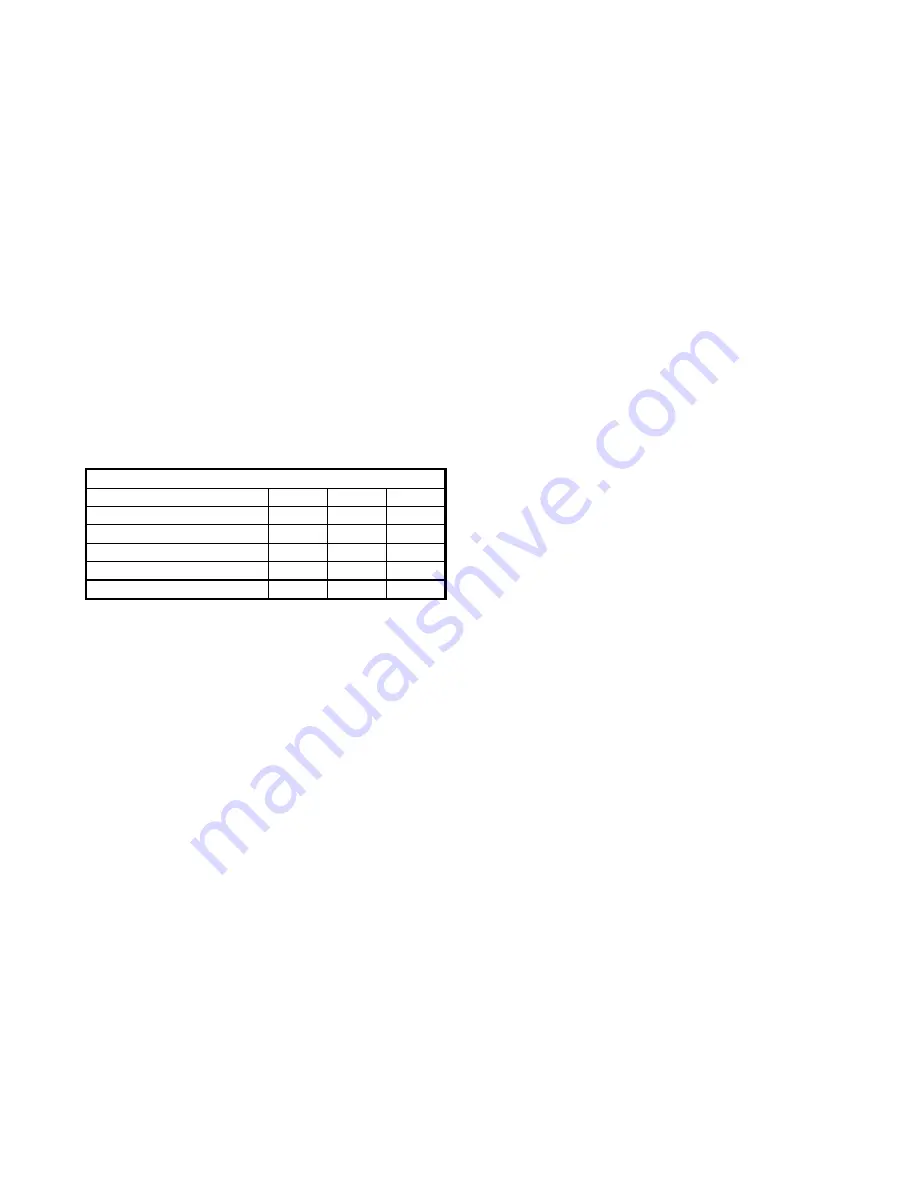

Control Register Bits 10, 9, and 8

IOS Model

Bit-10

Bit-9

Bit-8

Disabled

0

0

0

IOS-EP201

1

1

1

IOS-EP202

0

0

1

IOS-EP203

1

0

0

IOS-EP204

0

0

1

Bit-11 is reserved for factory testing. For normal operation this bit should

always be logic low.

Bit-15 can be used to issue a software reset. When bit-15 is set to a

logic high a software reset will occur.

Reading this register will return logic low on all data lines/bits except for

bits 11 to 8 which will reflect their last written state.

Input/Output Registers

(Read/Write) - (Base Addr + 02H to 06H)

Forty-eight possible input/output channels numbered 0 through 47 may

be individually accessed via these registers. The Input/Output Channel

registers are used to monitor/read or set/write channels 0 through 47. The

first eight channels are accessed at the carrier base a02H via the

low data byte. The next eight channels are accessed at the carrier base

a03H via the high data byte. The remaining 32 channels are

accessed similarly at the carrier base a offsets shown in Table 3.3.

If the Input/Output port is to be used as an output, you should first set the

output register bit as desired before setting the Direction Control register.

Note: if you select as an output port before setting this Input/Output register,

the output port will be logic low as this is the power-up/reset state of the

output register bits.

USER MODE

Table 3.4:

Control Register

Identification Bits