Functional Description

ARM DDI 0402F

Copyright © 2007-2010 ARM. All rights reserved.

2-11

ID011711

Non-Confidential

2.2

Functional operation

The functional operation is described in:

•

Timing

•

Bitmap mode

on page 2-13

.

2.2.1

Timing

A 60-bit instruction, loaded serially at the start of each test, controls the operation of the MBIST

controller.

Chapter 3

MBIST Instruction Register

describes how to write the instruction.

The timing diagrams in this section show the clock running at two different speeds:

•

the slower clock relates to the clock driven by your ATE

•

the faster clock relates to the clock driven by an on-chip

Phase Locked Loop

(PLL).

If you do not have an on-chip PLL, both clocks relate to the clock driven by your ATE.

Timing diagrams in the following sections show the procedures for operating the MBIST

controller:

•

Instruction load

•

Starting MBIST

•

Failure detection

on page 2-12

•

Data log retrieval

on page 2-12

.

Instruction load

To load an MBIST instruction, drive

MBISTSHIFT

HIGH. At the next rising clock edge, the

61-bit shift sequence begins as shown in

Figure 2-6

. To enable data input from the ATE, the PLL

is in bypass mode, and the clock is not running at test frequency.

Figure 2-6 Loading the MBIST controller instruction

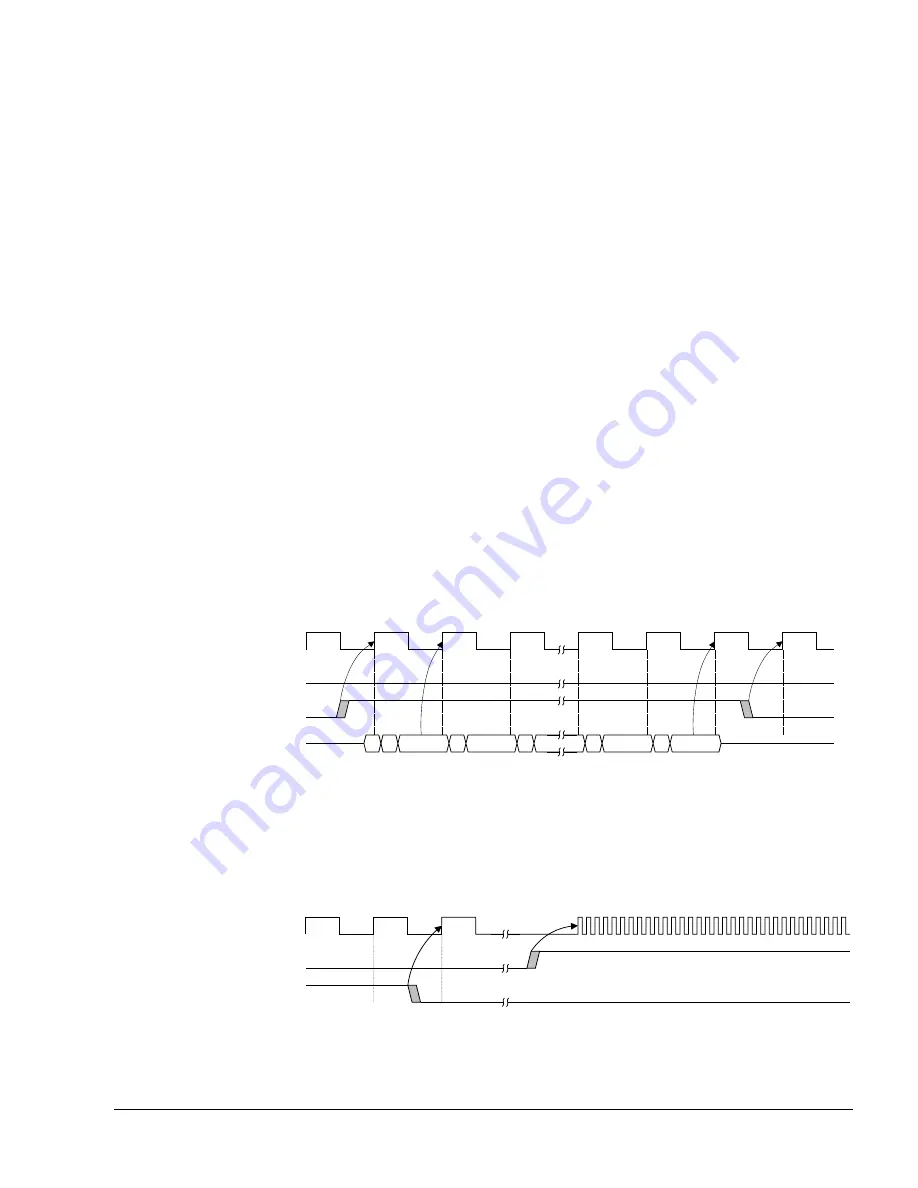

Starting MBIST

Reset the MBIST engine. After loading the MBIST instruction, drive

MBISTSHIFT

LOW and

disable

CLK

. With

CLK

disabled, drive

MBISTRUN

HIGH and, after an

MBISTRUN

setup

time, start the PLL at the test frequency as shown in

Figure 2-7

.

Figure 2-7 Starting the MBIST test

i[60]

i[59]

i[1]

i[0]

CLK

MBISTRUN

MBISTSHIFT

MBISTDATAIN

CLK

MBISTRUN

MBISTSHIFT