4

ROM’s which only occupies 256K bytes of the address space. The first 128K bytes are used by dBUG

and the second half is left for user. Refer to section 3.3.

The MC68HC901 is used as dBUG serial communication, baud rate generator, and ISA Bus interrupt

request. Refer to section 3.4.1.

The ISA Bus interface maps all the I/O space of the ISA bus to the MCF5204 memory at address

$04000000. Refer to section 3.6.

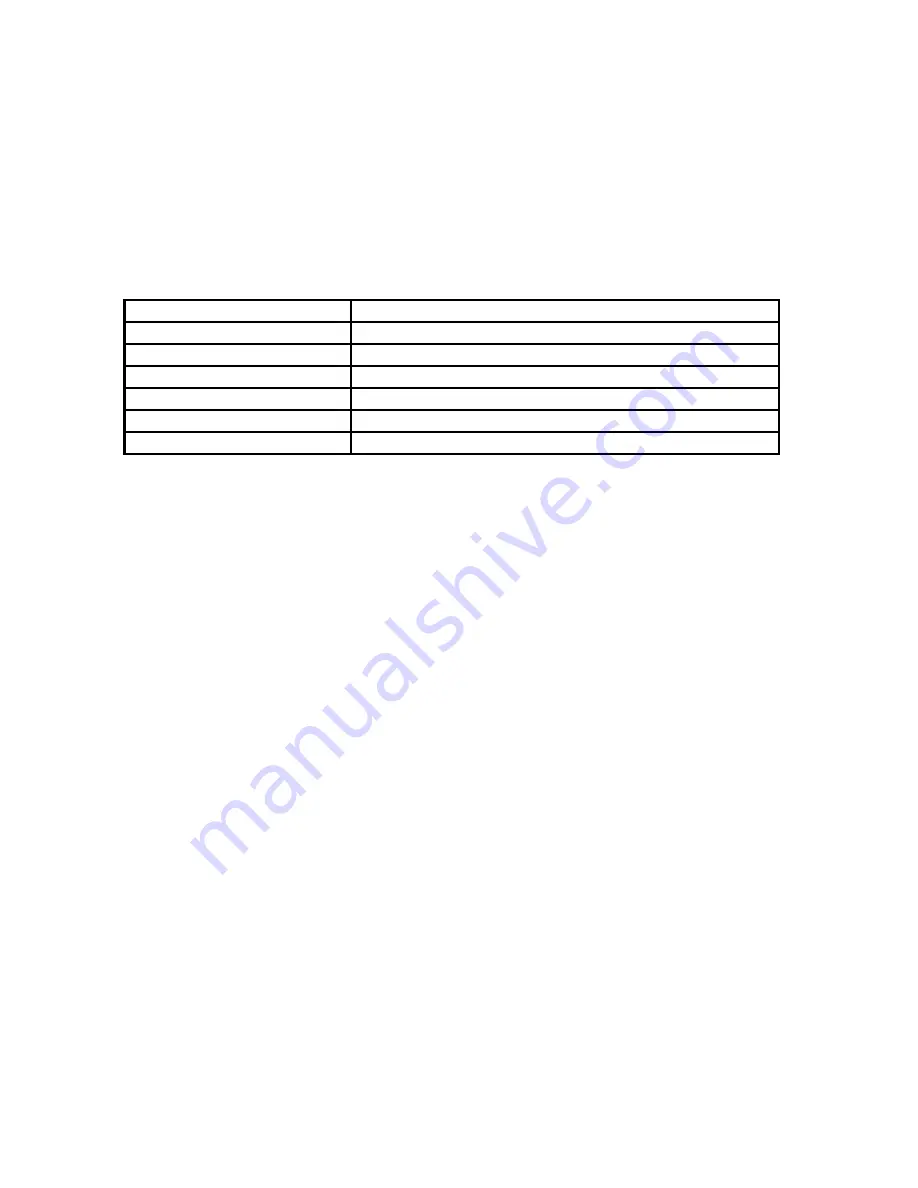

TABLE 3.1. The SBC5204 memory map.

ADDRESS RANGE

SIGNAL and DEVICE

$00000000-$000FFFFF1

-CS1, Up to 1M bytes of SRAM’s.

$01000000-$010003FF

Internal Module registers

$02000000-$020001FF

Internal SRAM

$03000000-$030FFFFF

-CS2, 1M space for MC68HC901. -CS3 is used for IACK

$04000000-$040FFFFF

-CS4, 1M ISA Bus area

$FFE00000-$FFE3FFFF

-CS0, 256K bytes of Flash ROM.

1 Refer to the text for more detail.

All the unused area of the memory map is available to the user.

3.1.8 Reset Vector Mapping

After reset, the processor attempts to get the initial stack pointer and initial program counter values from

locations $000000-$000007 (the first eight bytes of memory space). This requires the board to have a

nonvolatile memory device in this range with proper information. However, in some systems, it is preferred

to have RAM starting at address $00000000. In MCF5204, the -CS0 responds to any accesses after reset

until the V-bit is set for CS0. This includes the reset vector range. Since -CS0 is connected to Flash

ROM’s, the Flash ROM’s appear to be at address $00000000 which provides the initial stack pointer and

program counter (the first 8 bytes of the EPROM). The initialization routine, however, programs the chip-

select logic and locates the Flash ROM to start at $FFE00000 and the SRAM’s to start at $00000000.

3.1.9 DTACK Generation

The processor starts a bus cycle by providing the necessary information (address A1-A23, R/-W, etc.) and

asserting the -CS. The processor then waits for an acknowledgment (-DTACK) by the addressed device

before it can complete the bus cycle. This -DTACK is used not only to indicate the presence of a device, it

also allows devices with different access time to communicate with the processor properly. The MCF5204,

as part of the chip-select logic, has a built in mechanism to generate the -DTACK for all external devices

which do not have the capability to generate the -DTACK on their own. The Flash ROM’s and SRAM’s

can not generate the -DTACK. Their chip-select logic’s are programmed by dBUG to generate the -

DTACK internally after a preprogrammed number of wait states. In order to support the future expansion

of the board, the -DTACK input of the processor is also connected to the Processor Expansion Bus, J9.

This allows the expansion boards to assert this line to indicate their -DTACK to the processor. On the

expansion boards, however, this signal should be generated through an open collector buffer with no

pull-up resistor, a pull-up resistor is included on the board. All the -DTACK’s from the expansion boards

should be connected to this line.