22

ATtiny22/22L

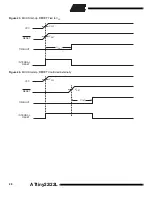

MCU Status Register - MCUSR

The MCU Status Register provides information on which reset source caused a MCU reset:

•

Bit 7..2 - Res: Reserved Bits

These bits are reserved bits in the ATtiny22/L and always read as zero.

•

Bit 1 - EXTRF: External Reset Flag

After a power-on reset, this bit is undefined (X). It will be set by an external reset. A watchdog reset will leave this bit

unchanged.

•

Bit 0 - PORF: Power-On Reset Flag

This bit is set by a power-on reset. A watchdog reset or an external reset will leave this bit unchanged.

To summarize, the following table shows the value of these two bits after the three modes of reset.

To make use of these bits to identify a reset condition, the user software should clear both the PORF and EXTRF bits as

early as possible in the program. Checking the PORF and EXTRF values is done before the bits are cleared. If the bit is

cleared before an external or watchdog reset occurs, the source of reset can be found by using the following truth table:

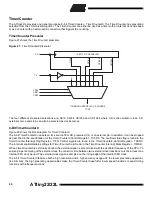

Interrupt Handling

The ATtiny22/L has two 8-bit Interrupt Mask control registers; GIMSK - General Interrupt Mask register and TIMSK -

Timer/Counter Interrupt Mask register.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all interrupts are disabled. The user

software can set (one) the I-bit to enable nested interrupts. The I-bit is set (one) when a Return from Interrupt instruction -

RETI - is executed.

When the Program Counter is vectored to the actual interrupt vector in order to execute the interrupt handling routine, hard-

ware clears the corresponding flag that generated the interrupt. Some of the interrupt flags can also be cleared by writing a

logic one to the flag bit position(s) to be cleared.

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared (zero), the interrupt flag will be set

and remembered until the interrupt is enabled, or the flag is cleared by software.

If one or more interrupt conditions occur when the global interrupt enable bit is cleared (zero), the corresponding interrupt

flag(s) will be set and remembered until the global interrupt enable bit is set (one), and will be executed by order of priority.

Note that external level interrupt does not have a flag, and will only be remembered for as long as the interrupt condition is

active.

Bit

7

6

5

4

3

2

1

0

$34 ($54)

-

-

-

-

-

-

EXTRF

PORF

MCUSR

Read/Write

R

R

R

R

R

R

R/W

R/W

Initial value

0

0

0

0

0

0

See bit description

Table 5. PORF and EXTRF Values after Reset

Reset Source

PORF

EXTRF

Power-On Reset

1

undefined

External Reset

unchanged

1

Watchdog Reset

unchanged

unchanged

Table 6. Reset Source Identification

PORF

EXTRF

Reset Source

0

0

Watchdog Reset

0

1

External Reset

1

0

Power-On Reset

1

1

Power-On Reset