ATtiny22/22L

38

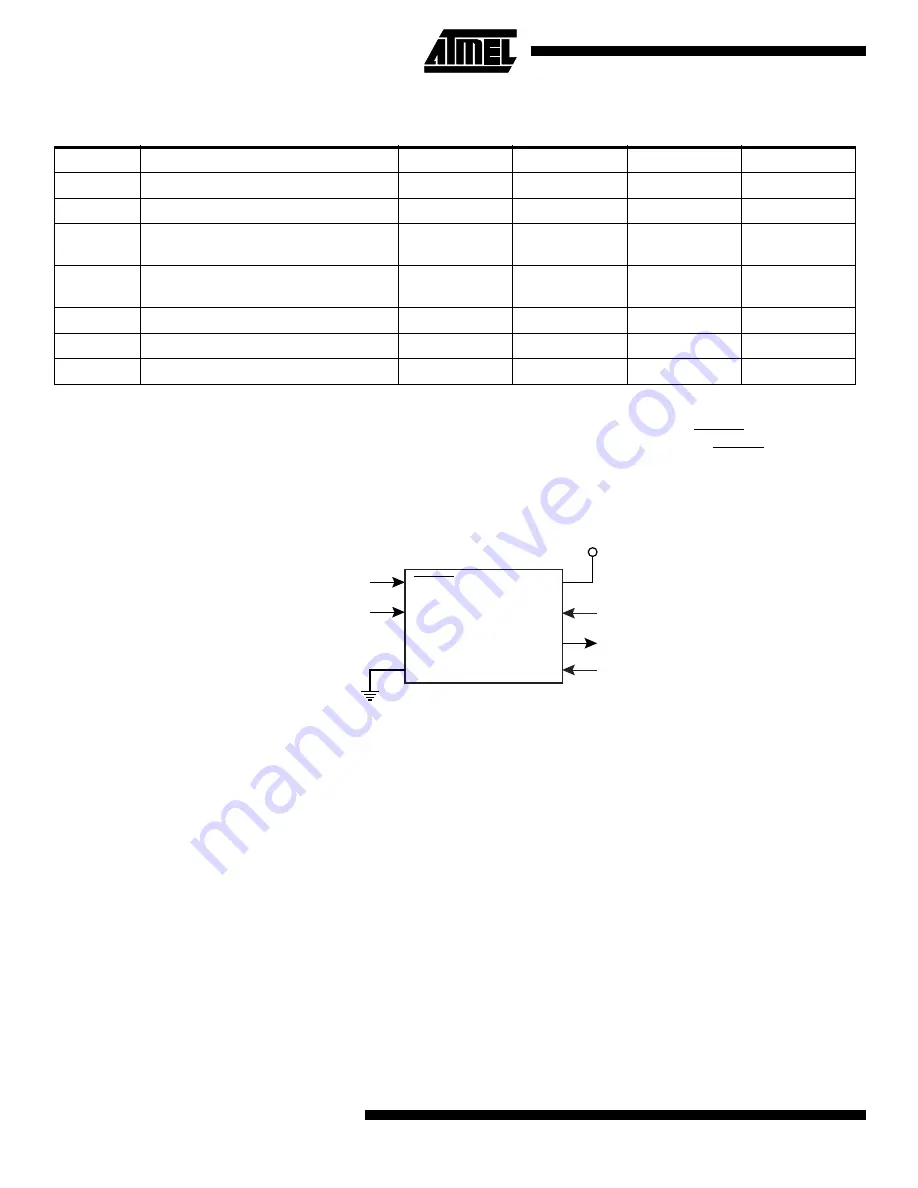

Low-Voltage Serial Downloading

Both the Program and Data memory arrays can be programmed using the serial SPI bus while RESET is pulled to GND.

The serial interface consists of pins SCK, MOSI (input) and MISO (output), see Figure 33. After RESET is set low, the

Programming Enable instruction needs to be executed first before program/erase instructions can be executed.

Figure 33. Low-voltage Serial Programming and Verify

For the EEPROM, an auto-erase cycle is provided within the self-timed write instruction and there is no need to first exe-

cute the Chip Erase instruction. The Chip Erase instruction turns the content of every memory location in both the Program

and EEPROM arrays into $FF.

The Program and EEPROM memory arrays have separate address spaces, $0000 to $03FF for Flash Program memory

and $000 to $07F for EEPROM Data memory.

Either an external clock is applied to the XTAL1/PB3 pin or the device must be clocked from the internal RC-oscillator. The

minimum low and high periods for the serial clock (SCK) input are defined as follows:

Low: > 2 MCU clock cycles

High: > 2 MCU clock cycles

Table 15. High-Voltage Serial Programming Characteristics

T

A

= 25

°

C ± 10%, V

CC

= 5.0V ± 10% (Unless otherwise noted)

Symbol

Parameter

Min

Typ

Max

Units

t

SHSL

SCI (PB3) Pulse Width High

100

ns

t

SLSH

SCI (PB3) Pulse Width Low

100

ns

t

IVSH

SDI (PB0), SII (PB1) Valid to SCI (PB3)

High

50

ns

t

SHIX

SDI (PB0), SII (PB1) Hold after SCI

(PB3) High

50

ns

t

SHOV

SCI (PB3) High to SDO (PB2) Valid

10

16

32

ns

t

WLWH_CE

Wait after Instr.3 for Chip Erase

5

10

15

ms

t

WLWH_PFB

Wait after Instr.3 for Write Fuse Bits

1.0

1.5

1.8

ms

RESET

XTAL1/PB3

GND

VCC

PB2

PB1

PB0

SCK

MISO

MOSI

CLOCK INPUT

2.7 - 6.0V

ATtiny22/L

GND