5. Connection Example with FreeScale iMX21

16

EPSON

S1R72V17 CPU Connection Guide

(Rev. 1.0)

5.2

iMX21 Bus Cycle Setting Example

•

iMX21 clock settings

The iMX21 clock settings are set as shown below in this connection example.

System clock: 264 MHz

CPU-IF bus clock (HCLK): 88 MHz (system clock 3 divisions)

•

Bus cycle settings

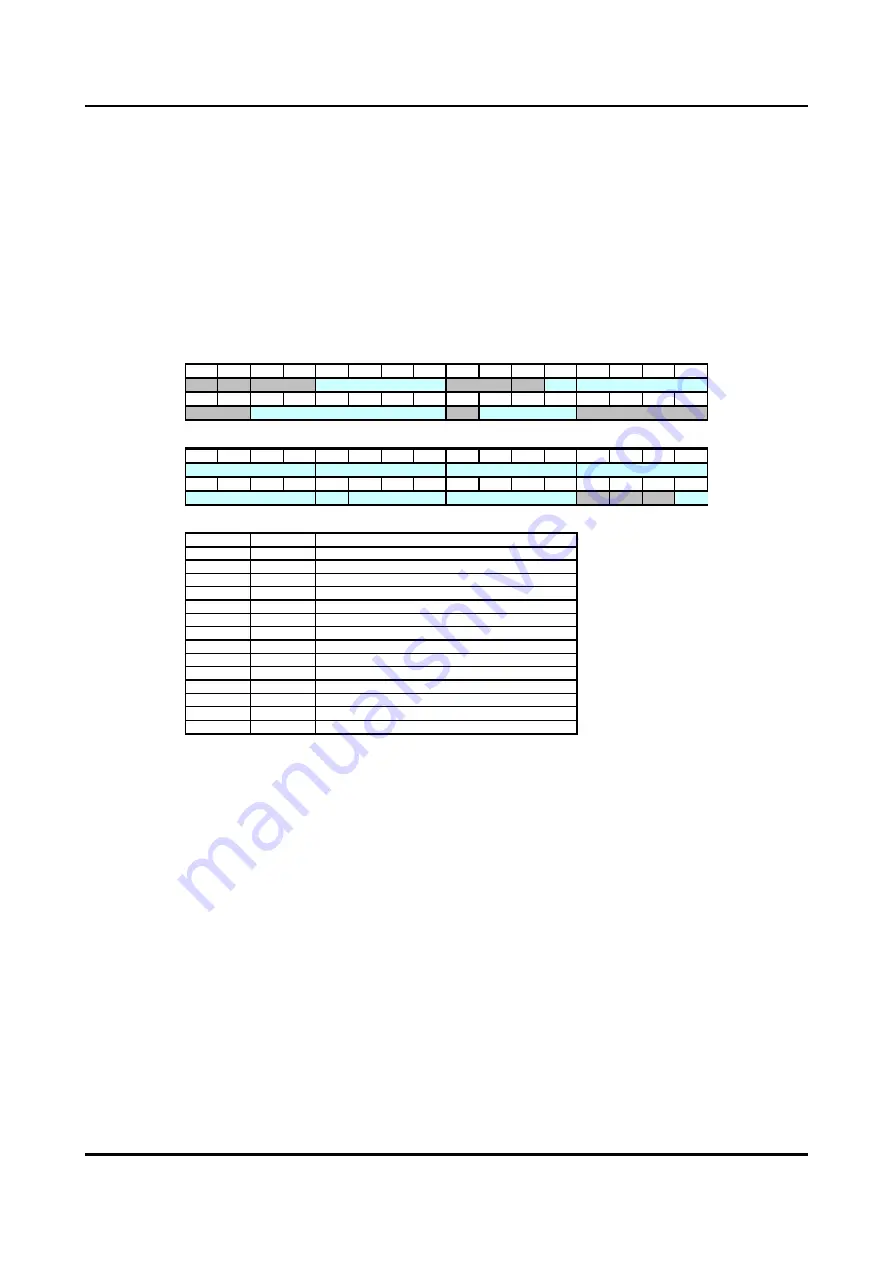

CS1U register (0xDF001008 address)

Setting: 0x0402_0700

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

SP

WP

PME SYNC

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

EW

CS1L register (0xDF00100C address)

Setting: 0x4200_0D01

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

EBC

PSR CRE WRAPCSEN

Setting descriptions

Register

Setting

Description

RWA

4'b0100

RW output assert timing (2HCLK)

SYNC

1'b0

Synchronous transfer mode (disabled)

RWN

4'b0010

RW output negate timing (1HCLK)

WSC

6'b000111

Access cycle (8HCLK)

WWS

3'b000

Wait cycle for write (0HCLK)

OEA

4'b0100

OE output assert timing (2HCLK)

OEN

4'b0010

OE output negate timing (1HCLK)

WEA

4'b0000

EBx output assert timing (0HCLK)

WEN

4'b0000

EBx output negate timing (0HCLK)

CSA

4'b0000

CS1 output assert timing (0HCLK)

EBC

1'b1

EB3, 2 output mode for read (disabled)

DSZ

3'b101

Data bus size (using 16 bits [15:0])

CSN

4'b0000

CS1 output assert timing (0HCLK)

CSEN

1'b1

CS1 enable (enabled)

DSZ

CSN

OEA

OEN

WEA

CSA

WEN

CNC

WSC

WWS

EDC

DCT

RWA

PSZ

RWN

Fig. 5-2 Bus cycle setting registers