PIC16C62B/72A

1998-2013 Microchip Technology Inc.

Preliminary

DS35008C-page 41

8.3

SSP I

2

C Operation

The SSP module in I

2

C mode fully implements all slave

functions, except general call support, and provides

interrupts on start and stop bits in hardware to support

firmware implementations of the master functions. The

SSP module implements the standard mode specifica-

tions, as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the

RC3/SCK/SCL pin, which is the clock (SCL), and the

RC4/SDI/SDA pin, which is the data (SDA). The user

must configure these pins as inputs or outputs through

the TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP

Enable bit SSPEN (SSPCON<5>).

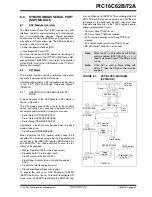

FIGURE 8-2:

SSP BLOCK DIAGRAM

(I

2

C MODE)

The SSP module has five registers for I

2

C operation.

These are the:

• SSP Control Register (SSPCON)

• SSP Status Register (SSPSTAT)

• Serial Receive/Transmit Buffer (SSPBUF)

• SSP Shift Register (SSPSR) - Not accessible

• SSP Address Register (SSPADD)

The SSPCON register allows control of the I

2

C opera-

tion. Four mode selection bits (SSPCON<3:0>) allow

one of the following I

2

C modes to be selected:

• I

2

C Slave mode (7-bit address)

• I

2

C Slave mode (10-bit address)

• I

2

C Slave mode (7-bit address), with start and

stop bit interrupts enabled for firmware master

mode support

• I

2

C Slave mode (10-bit address), with start and

stop bit interrupts enabled for firmware master

mode support

• I

2

C start and stop bit interrupts enabled for firm-

ware master mode support, slave mode idle

Selection of any I

2

C mode, with the SSPEN bit set,

forces the SCL and SDA pins to be operated as open

drain outputs, provided these pins are programmed to

inputs by setting the appropriate TRISC bits.

Additional information on SSP I

2

C operation may be

found in the PIC

®

MCU Mid-Range Reference Manual,

(DS33023).

8.3.1

SLAVE MODE

In slave mode, the SCL and SDA pins must be config-

ured as inputs (TRISC<4:3> set). The SSP module will

override the input state with the output data when

required (slave-transmitter).

When an address is matched or the data transfer after

an address match is received, the hardware automati-

cally will generate the acknowledge (ACK) pulse, and

load the SSPBUF register with the received value in the

SSPSR register.

There are certain conditions that will cause the SSP

module not to give this ACK pulse. This happens if

either of the following conditions occur:

a)

The buffer full bit BF (SSPSTAT<0>) was set

before the transfer was completed.

b)

The overflow bit SSPOV (SSPCON<6>) was set

before the transfer was completed.

In this case, the SSPSR register value is not loaded

into the SSPBUF, but bit SSPIF (PIR1<3>) is set.

Table 8-2 shows what happens when a data transfer

byte is received, given the status of bits BF and SSPOV.

The shaded cells show the condition where user soft-

ware did not properly clear the overflow condition. Flag

bit BF is cleared by reading the SSPBUF register, while

bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and

low for proper operation. The high and low times of the

I

2

C specification, as well as the requirement of the SSP

module, is shown in timing parameter #100, T

HIGH

, and

parameter #101, T

LOW

.

Read

Write

SSPSR reg

Match detect

SSPADD reg

Start and

Stop bit detect

SSPBUF reg

Internal

Data Bus

Addr Match

Set, Reset

S, P bits

(SSPSTAT reg)

RC3/SCK/SCL

RC4/

shift

clock

MSb

SDI/

LSb

SDA

Summary of Contents for PIC16C62B/72A

Page 4: ...PIC16C62B 72A DS35008C page 4 Preliminary 1998 2013 Microchip Technology Inc NOTES...

Page 30: ...PIC16C62B 72A DS35008C page 30 Preliminary 1998 2013 Microchip Technology Inc NOTES...

Page 38: ...PIC16C62B 72A DS35008C page 38 Preliminary 1998 2013 Microchip Technology Inc NOTES...

Page 48: ...PIC16C62B 72A DS35008C page 48 Preliminary 1998 2013 Microchip Technology Inc NOTES...

Page 80: ...PIC16C62B 72A DS35008C page 80 Preliminary 1998 2013 Microchip Technology Inc NOTES...

Page 104: ...PIC16C62B 72A DS35008C page 104 Preliminary 1998 2013 Microchip Technology Inc NOTES...

Page 110: ...PIC16C62B 72A DS35008C page 110 Preliminary 1998 2013 Microchip Technology Inc NOTES...

Page 120: ...PIC16C62B 72A DS35008C page 120 Preliminary 1913 Microchip Technology Inc...