AGB Programming Manual

System Configuration

©1999 - 2001 Nintendo of America Inc.

17

D.C.N. AGB-06-0001-002B4

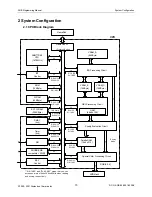

2.3 Memory Configuration and Access Width

DMA

CPU

Memory Type

Bus

Width

Read

Width

Write

Width

Read

Width

Write

Width

OAM

32

16/32

16/32

16/32

16/32

Palette RAM

16

16/32

16/32

16/32

16/32

VRAM

16

16/32

16/32

16/32

16/32

CPU Internal Working RAM

32

16/32

16/32

8/16/32

8/16/32

CPU External Working RAM

16

16/32

16/32

8/16/32

8/16/32

Internal registers

32

16/32

16/32

8/16/32

8/16/32

Game Pak ROM

(Mask ROM, Flash Memory)

16

16/32

16/32

8/16/32

16/32

Game Pak RAM

(SRAM, Flash Memory)

8

--

--

8

8

Good execution efficiency is obtained when programs that operate from the Game Pak

use 16-bit instructions (16-bit compiler), and those that operate from CPU Internal

Working RAM use 32-bit instructions (32-bit compiler).

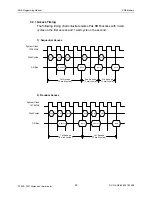

2.4 Little-Endian

In the AGB CPU, memory addresses are allocated in 8-bit increments, and little-

endian format is used in implementing the 8-, 16-, and 32-bit access widths.

A

B

C

D

0000h

0001h

0002h

0003h

Memory

Register

A

B

C

D

d31

d24

d23

d16 d15

d08

d07

d00