I2773-4.

4

en

211

Somat eDAQ

lite

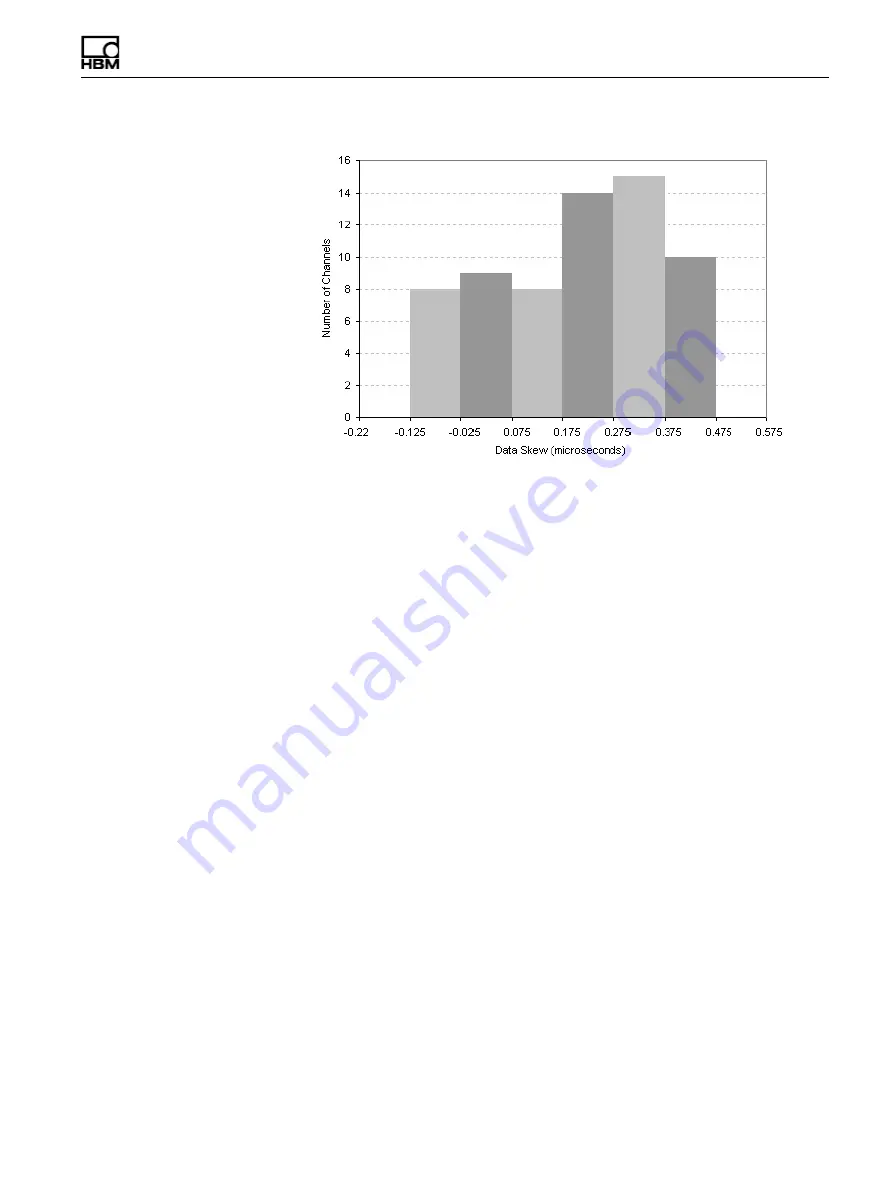

Figure 14-1:

Typical data skew distribution of 64 EHLS channels for several sample rates.

14.3

Digital Channel Synchronization

The ELDIO digital input channels are synchronized to the analog channels as closely

as possible. The eDAQ

lite

reads the state of the digital input status register for each

digital channel on each edge of the sample clock signal (i.e., when the analog channel

A/D converters are read). However, because the digital status registers are updated

when a digital input channel changes states, the precise time when a digital input

channel changes state is, in general, somewhere in between sample clock edges and

hence is not known exactly. Because of this, the digital input channels are expected to

lag the analog channels by about half of the sample period on average.

14.4

Resampled Channel Synchronization

Resampled channels include vehicle bus, serial bus, GPS and thermocouple channel

inputs. The common aspect of all of these channels is that the data is not sourced from

the MSR clock. As such, the data synchronization of these channels to the channels

that are sourced from the eDAQ

lite

MSR is always somewhat less deterministic.

The major issue in dealing with these channels is referred to as resampling. In general,

when the eDAQ

lite

reads and time stamps the data samples, the time stamps fall

somewhere between eDAQ

lite

sample periods. For example, for a thermocouple

channel output at 1.0 Hz, the input data samples almost always have fractional time

stamps such as 1.345 seconds or 3.360 seconds. The eDAQ

lite

runs its resampling

algorithm to generate data outputs (at one second intervals in this example).

While the specific details of the current resampling algorithm are beyond the scope of

this document, the general characteristics are as follows. First, the resampling function

is biased towards introducing a synchronization lead (i.e., the resampled time is

always less than or equal to the time stamp time). In the example case, the data output

associated with the 1.0 second time slot is set with the last data sample that has a time

stamp of at least 1.0 seconds and less than 2.0 seconds. Because of this, the

resampled channels can lead by up to one full sample period. If the data samples are

sourced at a much higher rate than the resampled output rate (e.g., 50 Hz to 1 Hz),

then the synchronization lead will be almost one full second consistently.

HBM: public

Summary of Contents for eDAQlite

Page 1: ...User Manual English Deutsch Espanol I2773 4 4 en HBM public Somat eDAQlite with TCE Software ...

Page 2: ...Somat eDAQlite 2 I2773 4 4 en HBM public ...

Page 16: ...Somat eDAQlite 16 I2773 4 4 en HBM public ...

Page 22: ...Somat eDAQlite 22 I2773 4 4 en HBM public ...

Page 88: ...Somat eDAQlite 88 I2773 4 4 en HBM public ...

Page 106: ...Somat eDAQlite 106 I2773 4 4 en HBM public ...

Page 128: ...Somat eDAQlite 128 I2773 4 4 en HBM public ...

Page 190: ...Somat eDAQlite 190 I2773 4 4 en HBM public ...

Page 202: ...Somat eDAQlite 202 I2773 4 4 en HBM public ...

Page 222: ...Somat eDAQlite 222 I2773 4 4 en HBM public ...

Page 224: ...Somat eDAQlite 224 I2773 4 4 en HBM public ...