83-517-000 Rev.

A

69

Service Request: Enable and Event Registers

7.8.3

The Conditional Registers are continuously monitored. When a change is detected in a register bit which is

enabled, the power supply will generate an

SRQ

message.

The

SRQ

message is: “

!nn

” terminated by

CR

, where the

“

nn

” is the power supply Address. The

SRQ

will be

generated either in Local or Remote mode. Refer to Tables 7-9 to 7-12 for details of the Enable and Event

Registers.

7.8.3.1

Fault Enable Register

The Fault Enable Register is set to the enable fault

SRQ

’s

.

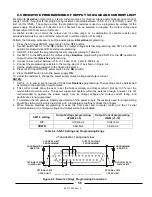

Table 7-9: Fault Enable Register

7.8.3.2

Fault Event Register

The Fault Event will set a bit if a condition occurs and it is Enabled. The register is cleared when

FEVE?

,

CLS

or

RST

commands are received.

BIT

Enable

bit name

Fault symbol

Bit Set condition

Bit reset condition

0 (LSB)

Spare bit

SPARE

Fault condition

occurs and it is

enabled.

The fault can set a

bit, but when the

fault clears the bit

remains set.

Entire Event Register is

cleared when user sends

“

FEVE?

” command to read

the register.

“

CLS

” and AC Input power-up

also clear the Fault Event

Register. (The Fault Event

Register is not cleared by the

RST

command)

1

AC Fail

AC

2

Over-Temperature

OTP

3

FOLD

back

FOLD

4

Over-Voltage

OVP

5

Shut-Off

SO

6

Output OFF

OFF

7(MSB)

Enable

ENA

Table 7-10: Fault Event Register

BIT

Enable

bit name

Fault symbol

Bit Set condition

Bit reset condition

0 (LSB)

Spare bit

SPARE

User command:

“

FENA nn

” where

“

nn

”

is

hexadecimal

User command: “

FENA nn

”

where

“

nn

” is hexadecimal. If

nn

=”00”, no fault

SRQ

’s

will be

generated.

1

AC Fail

AC

2

Over-Temperature

OTP

3

FOLD

back

FOLD

4

OverVoltage

OVP

5

Shut-Off

SO

6

Output OFF

OFF

7(MSB)

Enable

ENA