ACCES I/O Products, Inc.

MADE IN THE USA

mPCIe-AIO16-16F Family Manual

5

Rev 01

EXT:

If EXT is SET then an IRQ has been fired from the DIO13 Secondary Function “External IRQ”. Refer to DIO Control (+48) for de

tails on DIO Secondary Functions.

LDAC:

If LDAC is SET then an IRQ has been fired from the DIO12 Secondary Function “LDAC”. Refer to DIO Control (+48) for details o

n DIO Secondary Functions.

FOF:

If FOF is SET then an IRQ has been fired because the ADC FIFO has Overrun: More data was acquired than fit in the ADC FIFO.

FAF:

If FAF is SET then an IRQ has been fired because the ADC FIFO Count (+28) has reached the configured FIFO Almost Full IRQ Threshold (+20).

DTO:

If DTO is SET then a DMA Timeout IRQ has been fired.

DDONE:

If DDONE is SET then a DMA Done IRQ has been fired.

ADCSTART:

If ADCSTART is SET then an IRQ has been fired from the DIO14 Secondary Function “ADCSTART”. Refer to DIO Control (+48) for d

etails on DIO Secondary

Functions.

ADCTRIG:

If ADCTRIG

is SET then an IRQ has been fired from the DIO15 Secondary Function “ADCTRIG”. Refer to DIO Control (+48) for details on DIO

Secondary

Functions.

Bits D7 through D0 indicate if the corresponding IRQ has been enabled.

Write IRQ Status bits SET to clear the latched IRQ Status bit(s). Typically, code will read +40 and write the value to +40 to clear all detected IRQs and leave the IRQ enables unchanged.

Write IRQ Enable bits SET to enable corresponding IRQ sources.

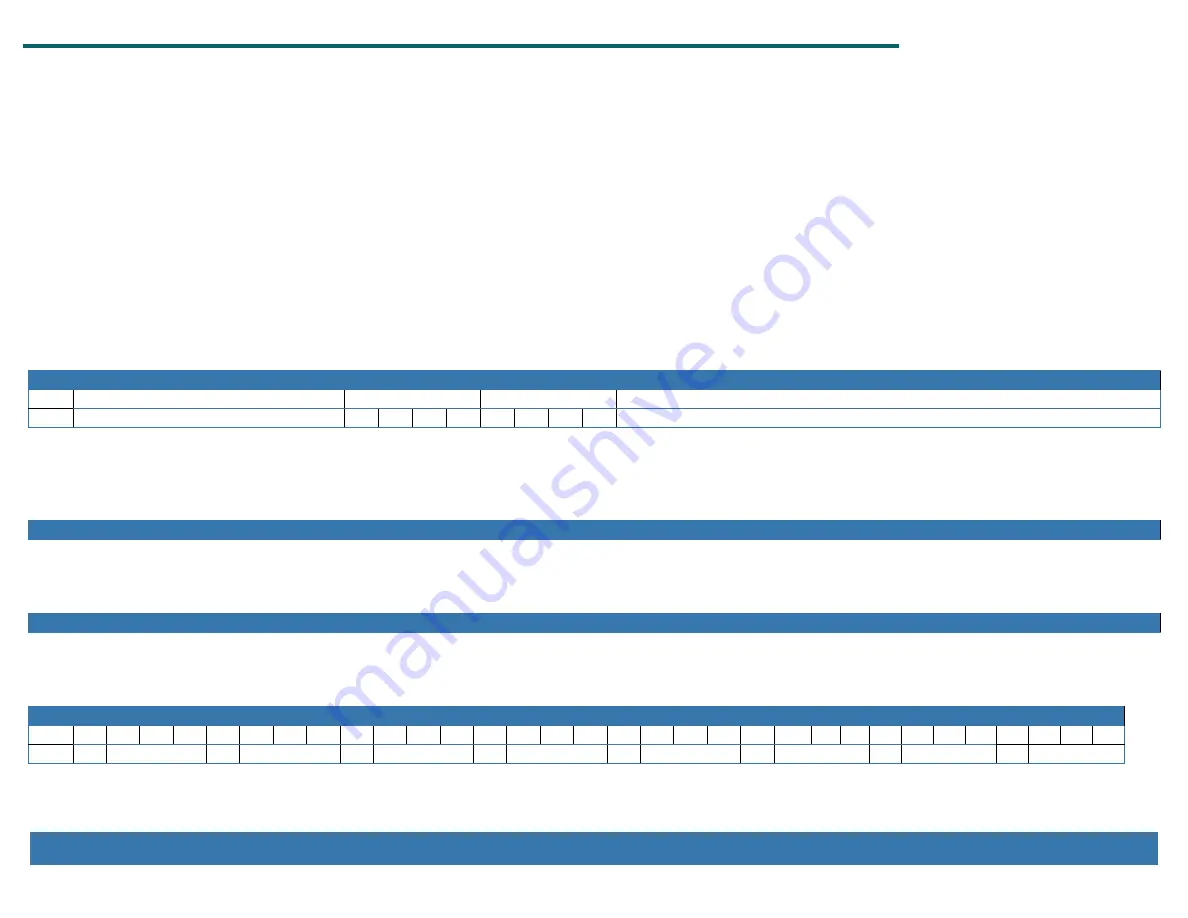

DAC Control, 4 of 32-bit Memory BAR[1]Read/Write 32-bits only

bit D31 through D24

D23 through D20

D19 through D16

D15 through D0

Name UNUSED

C3 C2

C1

C0

A3 A2 A1 A0 16-bit DAC Counts (0-FFFF)

Please refer to the LTC1664 Data Sheet for details.

Consult the AIOAIO Software Reference, or our sample programs’ source, to avoid the hassle:

DAC_SetRange1(iBoard, iChannel, iRange);

DAC_OutputV(iBoard, iChannel, double Voltage);

ADC Base Clock, C of 32-bit Memory BAR[1]Read Only 32-bits only

ADC Base Clock: Reading this 32-bit register returns the speed (in Hertz) of the clock used to generate ADC Start Conversions. Typical value is 125Million (125MHz), but for

broadest compatibility software should always read this register during init, and always use the read value when calculating what, if any, divisor to write to the

ADC Rate Divisor register.

ADC Rate Divisor, 10 of 32-bit Memory BAR[1]Read/Write 32-bits only

ADC Rate Divisor: Write a 32-bit divisor to the ADC Rate Divisor register to control the speed at which ADC Conversions occur in selected ADC Conversion Start Modes.

Actual ADC Start Rate (Hz) = ADC Base Clock ÷ ADC Rate Divisor

ADC Rate Divisor = integer(ADC Base Clock ÷ Target ADC Start Rate)

ADC Advanced Sequencer Gain Control, 18 of 32-bit Memory BAR[1]Read/Write 32-bits only

bit D31 D30 D29 D28 D27 D26 D25 D24 D23 D22 D21 D20 D19 D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

Name RSV AIN 7 GAIN2:0 RSV AIN 6 GAIN2:0 RSV AIN 5 GAIN2:0 RSV AIN 4 GAIN2:0 RSV AIN 3 GAIN2:0 RSV AIN 2 GAIN2:0 RSV AIN 1 GAIN2:0 RSV AIN 0 GAIN2:0

Each nybble configures the gain of the corresponding Analog Input channel ONLY when the ADC is running in Advanced Sequenced mode.