REGISTERS

Copyright 2017

6-13

FibreXtreme Hardware Reference

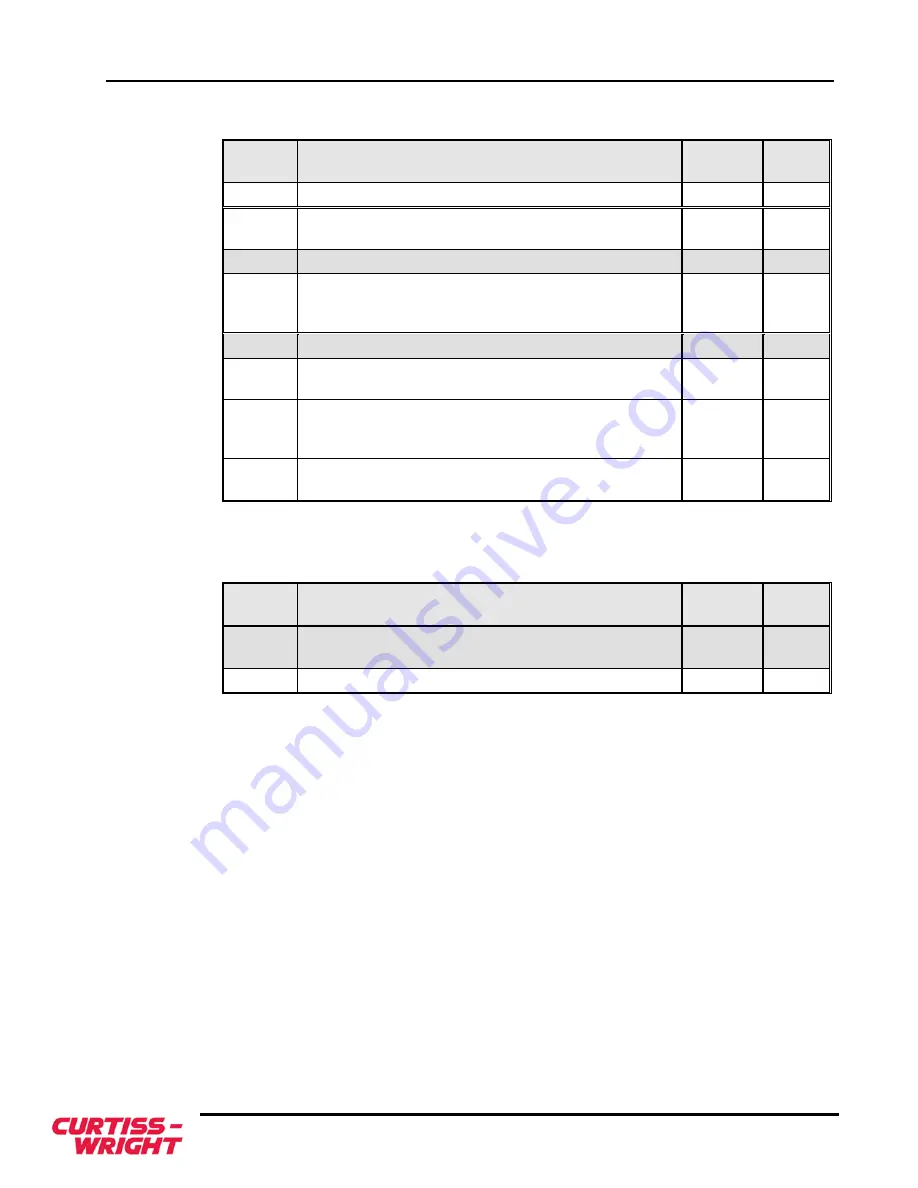

Send Chain Length/Flags (CLENFLGS0) – Offset 0x48

Field

Description

Access

Reset

Value

23 to 0

Length of buffer in 32-bit words.

R/W

0

24

End Chain

– Write ‘1’ to say this is the last chain entry.

Write ‘0’ if it is not.

R/W

0

25

Reserved.

None

0

27 to 26

Data Swapping

– “00” for straight, “01” to swap bytes,

“10” to swap 32-bit words, “11” to swap 32-bit words

and bytes.

R/W

0

28

Reserved.

None

0

29

Interrupt

– Write ‘1’ to interrupt on transfer complete,

Write ‘0’ otherwise.

R/W

0

30

Go

– Set to ‘1’ to start this transaction, ‘0’ to stop it. If it

is a chained transaction, the first action is to fetch the

chain entry.

R/W

0

31

Done

– A ‘1’ indicates this channel is currently idle.

A ‘0’ indicates a DMA is in progress.

R

0

Send Next Chain Entry (CNEXT0) – Offset 0x4C

Field

Description

Access

Reset

Value

3 to 0

Reserved (Lower four bits of PCI address must be

zero).

None

0

31 to 4

PCI address for the next chain entry.

R/W

0

Summary of Contents for FHF5-PC4MWB04-00

Page 2: ......

Page 8: ...Copyright 2017 iv FibreXtreme Hardware Reference ...

Page 26: ......

Page 40: ......

Page 48: ...SPECIFICATIONS Copyright 2017 5 8 FibreXtreme Hardware Reference ...

Page 50: ......

Page 68: ......

Page 74: ......

Page 76: ......

Page 78: ......

Page 84: ......

Page 86: ......

Page 96: ......