NCO-Related Registers

4-11

MASK_SYNCOK

1

If this bit is 1, a missing SYNCOK does not generate an

interrupt. If this bit is 0, a missing SYNCOK generates an

interrupt. The reset value is 0.

MASK_FIFO_ALARM

0

If this bit is 1, a FIFO alarm (pointer collision) does not

generate an interrupt. If this bit is 0, a FIFO alarm

(pointer collision) generates an interrupt. The reset value

is 0.

4.2.2 Register 13

RES

Reserved

R 7

This bit is reserved.

BELOW_THRES

FIFO CONTENT THRESHOLD

R 6

When this bit is 1, the virtual FIFO content is below or

equal to the threshold programmed in Register 43.

During AUTO_ACQUISITION, the threshold is

dynamically changed. The reset value is 0.

MEASUREMENT_DONE

R 5

A 1 in this bit indicates that the measurement data gained

during byte clock probe are valid and that the

measurement is complete. The reset value is 0.

STEP_UPDATE

R 4

A 1 in this bit indicates a step update since the last

reading of the register. This is relevant only during NCO

acquisition mode. The reset value is 0.

AUTO_ACQUI_RUNNING

R 3

A 1 in this bit indicates that the internal frequency

acquisition is running. The reset value is 0.

ACQ_STATE

Internal Acquisition State

R [2:0]

This indicates how many auto acquisition loops have

taken place since the initiation of the auto acquisition

mode. The reference duration has a length of two

ACQ_STATE input packets, and the threshold is divided

by two ACQ_STATE times. The reset value is 0b111.

7

6

5

4

3

2

0

RES

BELOW_

THRES

MEASUREMENT_

DONE

STEP_

UPDATE

AUTO_ACQUI_

RUNNING

ACQ_STATE

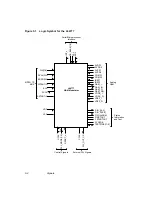

Summary of Contents for L64777

Page 1: ...L64777 DVB QAM Modulator Order Number I14031 A Technical Manual June 2000...

Page 10: ...x Contents...

Page 14: ...1 4 Introduction...

Page 90: ...5 10 Signals...

Page 110: ...A 8 Programming the L64777 in Serial Host Interface Mode...

Page 116: ...C 2 Monitoring Device Internal Signals...

Page 124: ......