Programming

Chapter 5

SCXI-1100 User Manual

5-2

© National Instruments Corporation

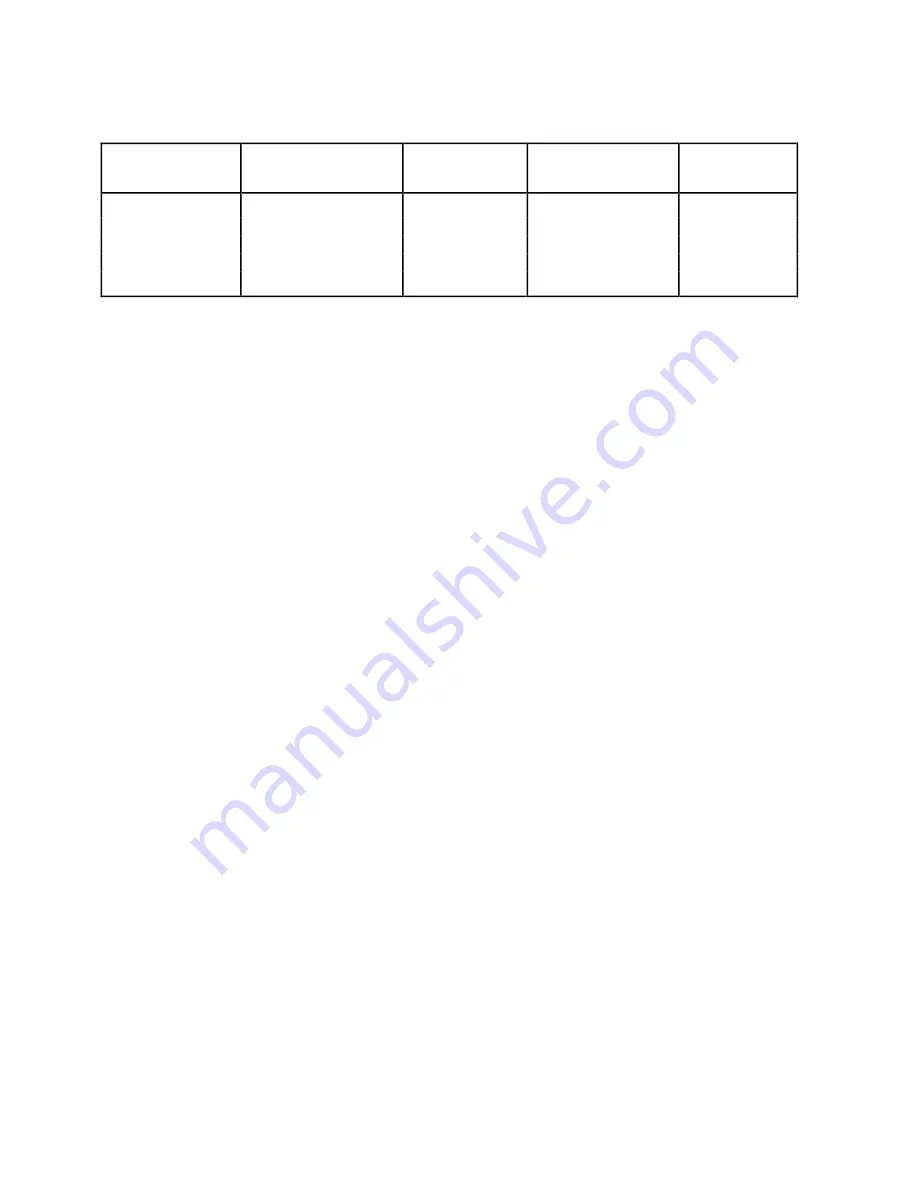

Table 5-1. SCXI-1100 Rear Signal Connector Pin Equivalences

SCXIbus Line

SCXI-1100 Rear

Signal Connector

MIO Boards

Lab Boards

PC-LPM-16

MOSI

SERDATIN

ADIO0

PB4

DOUT4

D*/A

DAQD*/A

ADIO1

PB5

DOUT5

INTR*

SLOT0SEL*

ADIO2

PB6

DOUT6

SPICLK

SERCLK

EXTSTROBE*

PB7

DOUT7

MISO

SERDATOUT

BDIO0

PC1

DIN6

Register Selection and Write Procedure

1. Select the slot of the module to be written to (or Slot 13 or 14). Initial conditions:

SERDATIN = X.

DAQD*/A = X.

SLOT0SEL* = 1.

SERCLK = 1.

2. Clear SLOT0SEL* to 0 to deassert all SS* lines to all modules in all chassis.

3. For each bit, starting with the MSB (bit 15):

a. Set SERDATIN = bit to be sent. These bits are the data that is being written to the

Slot-Select Register.

b. Clear SERCLK to 0.

c. Set SERCLK to 1. This rising edge clocks the data. (If you are using an MIO board,

writing to the EXTSTROBE* register will pulse EXTSTROBE* low and then high,

accomplishing steps 3b and 3c.)

4. Set SLOT0SEL* to 1. This asserts the SS* line of the module whose slot number was

written to Slot 0. If you are using multiple chassis, only the appropriate slot in the chassis

whose address corresponds to the written chassis number is automatically selected. When no

communication is taking place between the data acquisition board and any modules, write

zero to the Slot-Select Register to ensure that no accidental writes occur.

5. If you are writing to a Configuration Register, clear DAQD*/A to 0 (this indicates data is

written to the Configuration Register). If you are writing to the HSCR or the FIFO Register,

leave DAQD*/A high.

6. For each bit to be written to the Configuration Register:

a. Establish the desired SERDATIN level corresponding to this bit.

b. Clear SERCLK to 0.

c. Set SERCLK to 1 (clock the data). (If you are using an MIO board, writing to the

EXTSTROBE* register pulses EXTSTROBE* low and then high, accomplishing

steps 6b and 6c.)